Het analoge schermergebied van digitale electronica

Digitale schakelingen zijn ongemeen populair. Het werken met "1" en "0" blijkt voor mens en IC heel wat aantrekkelijker te zijn dan de omgang met ruis, brom en oscillaties die onlosmakelijk met analoge technieken verweven lijken te zijn. Toch is de eenvoud van "1" en "O" betrekkelijk Ook digitale IC's hebben typisch analoge kenmerken zoals in- en uitgangsimpedantie en voor goed digitaal ontwerpen is ook zeker van deze aspekten kennis noodzakelijk.

Waarom zijn digitale technieken zo in trek? Natuurlijk zijn daarvoor vele technische redenen aan te voeren, maar we geloven dat de verklaring hiervoor deels in het psychologische vlak gevonden kan worden. Een aspirant elektronicus zal na de nodige wiskundige stoeipartijen met analoge schakelingen, opgelucht ademhalen bij de kennismaking met de logische poort. Nul is nul en een is een. Digitale elektronica is nu eenmaal veel beter te vangen in een abstraktie waarmee de grijze massa overweg kan. Ook een computer weet met zo'n duidelijk gedefinieerd en eenvoudig rekenmodel natuurlijk beter raad. Niet voor niets waren de eerste simulatieprogramma's bedoeld voor het doorrekenen van logische schakelingen.

In feite bestaan digitale schakelingen natuurlijk ook uit een verzameling transistoren en werken ze niet met enen en nullen maar met spanningen en stromen (overigens ook weer een abstraktie). Kennis van deze fysieke eigenschappen is voor een goed digitaal ontwerp beslist nodig. Voor de verbindingen met de buitenwereld, maar ook als digitale poorten "misbruikt" worden als bijvoorbeeld AMV's of MMV's, is kennis van het elektrisch gedrag bittere noodzaak.

Familiegeschiedenis

Dat het leven vroeger eenvoudiger was, geldt zeker voor elektronica. De 7400-serie was de meest toegepaste standaard-logica en mag zich stamhouder van de logica in IC-vorm noemen. De 7400-serie is gebaseerd op bipolaire IC-technologie en werkt met in verzadiging gestuurde transistoren. Het belangrijkste kenmerk is het asymmetrische gedrag van in-en uitgangen, een behoorlijk groot stroomverbruik en de vaste voedingsspanning van 5 V.

Als tegenhanger werd de 4000-serie gelanceerd, die in zeer stroomzuinige CMOS-technologie vervaardigd werd. Het (statische) stroomverbruik van deze IC's is nagenoeg nul en het voedingsspanningsbereik is veel ruimer (3 ... 18 V). Wat snelheid betreft moest de 4000-serie het afleggen tegen TTL als de schildpad tegen de haas.

In het bipolaire kamp werkte de hete CMOS-adern als een katalysator op de ontwikkelaars. Men begreep dat voor voldoende konkurrentiekracht het toch wel erg hoge stroomverbruik van TTL gereduceerd diende te worden: low power schottky-TTL (LS-TTL) werd als nieuwe troef in de strijd geworpen. Nog steeds bipolaire transistortechniek in deze serie, maar met kunstgrepen werd ervoor gezorgd dat transistoren minder ver in de verzadiging gestuurd werden. Hierdoor kon de TTL-snelheid gehandhaafd blijven bij een belangrijk geringer stroomverbruik. Voor de CMOS-fans en fabrikanten zag het er niet goed uit. TTL leek de standaard te worden. De sterk opkomende computerindustrie stelde hogere eisen aan snelheid dan aan stroomverbruik en koos ook (LS)TTL.

Bij de introduktie van de nieuwe high speed CMOSserie werd de strategie veranderd naar het model van Troje. Deze nieuwe IC's werden vermomd met een 74)0C-stempel waarin het tussenvoegsel HC (High speed CMOS) of HCT (TTLkompatibel) werd opgenomen. Funktioneel sluit de HC- en HCT-serie aan op de normale TTL-serie. Het is echter belangrijk om te beseffen dat deze nieuwe 74-series elektrisch gezien geen TTL-gedrag vertonen. De HC en HCT-logica kombineert de snelheid van LSTTL met een nog lager (statisch) stroomverbruik dan dat van de 4000-serie en wint om die reden dan ook snel aan populariteit. Deze stijgende ster is zeker niet in de laatste plaats te danken aan de mogelijke uitwisselbaarheid met standaard-TTL. Overigens worden populaire IC's uit de oorspronkelijke 4000-serie (bijvoorbeeld 4049, 4060, 4066, 4511) ook vervaardigd in een 74HC(T)-variant.

Ingangsperikelen

Uit het voorstaande blijkt dat er, funktioneel bezien, een grens loopt in logica-land tussen de 74)0C-serie en de 40XX-serie. Bij beschouwing van de elektrische eigenschappen moet deze grens echter anders getrokken worden en wel tussen de toegepaste technologieën: enerzijds bipolair met als belangrijkste vertegenwoordigers 74XX en 74LSXX en anderzijds CMOS: 40XX, 74HCXX en 74HCTXX.

Het kruciale verschil tussen deze families is dat bipolaire logica wat betreft in- en uitgangsgedrag asymmetrisch is, zowel voor stroom als voor spanning, terwijl CMOS in principe symmetrisch is. We schrijven in principe, want bij de HCTserie zijn met opzet aan de ingang de spanningsnivo's aangepast op die van de bipolaire TTL.

"Gewone" TTL wordt, ten behoeve van de snelheid, geschakeld op de emitter(s) van de ingangstransistor (1a). Is de ingang "hoog"; dan loopt er nauwelijks stroom; de ingangstransistor spert. Wordt de ingang "laag'; dan moet echter een niet onaanzienlijke emitterstroom opgenomen worden. Om een ingang gedefinieerd laag te maken, moet bovendien de spanning behoorlijk laag zijn (< 0,7V). Juist vanwege de relatief grote sink-stroom is dat niet altijd even eenvoudig. Een weerstand naar massa zal relatief laagohmig moeten zijn. Een TTL-ingang "hoog" maken met een pull-up-weerstand is veel eenvoudiger en kan met een veel hoogohmigere weerstandswaarde.

Figuur 1. Mogelijke TTLingangskonfiguraties.

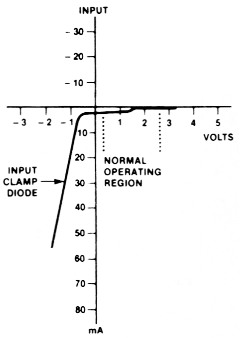

LS-TTL-ingangen zijn weliswaar niet verbonden met de emitter van de ingangstransistor (figuur 1b . . . 1d), maar gedragen zich elektrisch hetzelfde als gevolg van een interne pull-up-weerstand. In figuur 2, de ingangskarakteristiek, is de asymmetrische ingangsstroom goed te zien. In het derde kwadrant (ingang negatief ten opzichte van massa) is de karakteristiek van de ingangsklamp-diode te herkennen. CMOS-ingangen gedragen zich elektrisch geheel anders. De ingangen zijn via eeq protektienetwerk verbonden met de gates van ingangs-MOS-FET's waardoor deze zeer hoogohmig zijn. De ingangsstroom bestaat uit alleen een zeer kleine lekstroom.

Figuur 2. TTL-ingangskarakteristieken. De stroom nodig om een ingang laag te maken, is veel groter dan om hem hoog te maken.

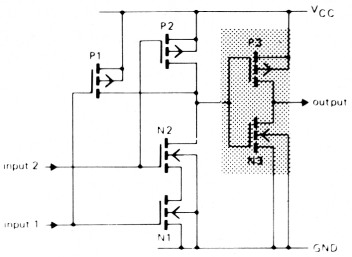

Bij CMOS (4000- en 74HC-serie) ligt het schakelnivo op de helft van de voedingsspanning; ook in dit opzicht is de ingang dus symmetrisch. Bij de HCT-serie is het schakelnivo aangepast op dat van TTL. De in het grijze kader aangegeven komponenten in figuur 3b zijn hiervoor verantwoordelijk. Een "hoge" LS-TTL-uitgang geeft worst case een spanning van slechts 2,4 V af. Een gewone CMOS-ingang zou deze spanning al als "laag" interpreteren. Bij HCT zorgt een interne level-shiftdiode (D3 in figuur 3b) ervoor dat het schakelnivo naar onderen wordt verschoven naar 1,4 V in plaats van 2,5 V (bij Vcc = 5 V). Wanneer de ingang nu "laag" wordt zou ten gevolge van deze diode P3 niet goed uit geleiding gaan, waardoor de voeding extra belast zou worden. Om dit euvel te ondervangen, is een extra pull-up-transistor toegevoegd (P2) die in geleiding komt als de ingang laag wordt.

Figuur 3. CMOS-ingangen zijn zeer hoogohmig.

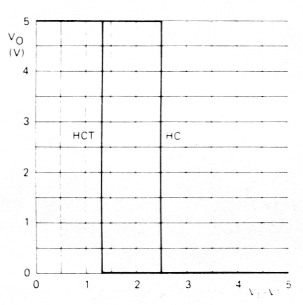

Het enige verschil tussen HC en HCT is deze verschuiving in schakelnivo's aan de ingang (figuur 4). De statische ingangsstroom blijft, ongeacht het nivo op de ingang, bijzonder klein. De opgenomen voedingsstroom blijkt echter ook nog een funktie te zijn van de aangeboden ingangsspanning. Bij vanuit (LS)TTL aangestuurde HC(T)MOS moet hiermee rekening worden gehouden.

Figuur 4. Overdrachtskarakteristiek van CMOS, HC en HCT.

Uitgangsbeslommeringen

TTL-uitgangen zijn er in een aantal konfiguraties (figuur 5) met elk zijn specifieke voordelen. Vrij algemeen is een push-pull-trap (totem pole), waaraan soms nog een diode is toegevoegd. Indien zo'n diode aanwezig is, kan met een externe pull-up-weerstand het hoog-uitgangsnivo boven de voedingsspanning getrokken worden, hetgeen overigens ook geldt voor open-kollektor-uitgangen (5e).

Figuur 5. TTL-uitgangen: heel wat mogelijkheden.

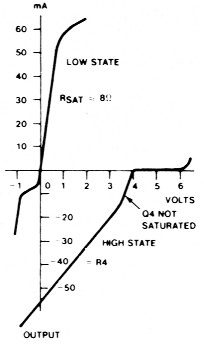

Figuur 6. TTL-uitgangskarakteristiek Stroom sinken gaat TTL beter af dan sourcen.

Uit die uitgangskonfiguraties blijkt ook dat TTL wel bestand is tegen kortsluiting van de uitgang naar massa (de interne weerstand zorgt voor voldoende stroombegrenzing), maar niet tegen kortsluiting naar de plus.

Bij CMOS-uitgangen bestaat dit onderscheid niet. Het uitgangsgedrag van een "hoge" uitgang is min of meer gelijk (of eigenlijk komplementair) met dat van een lage uitgang. Deze gelijkheid is ook te begrijpen als we de symmetrische opbouw van een (gebufferde) CMOS-uitgang bekijken (figuur 7). Een ander aspekt van een CMOS-uitgang is dat deze zich in zekere zin als een stroombron gedraagt (figuur 8). De uitgangsstroom is daarbij sterk afhankelijk van de voedingsspanning omdat hieraan de interne gate-spanning van de uitgangstransistoren gerelateerd is. Ook bestaat een sterke temperatuurafhankelijkheid van de uitgangsstroom.

Figuur 7. CMOS-uitgangen zijn symmetrisch van opbouw. Bij ongebufferde CMOS ontbreekt het omkaderde gedeelte.

Figuur 8. De symmetrie van CMOS komt ook tot uitdrukking in de uitgangskarakteristiek.

De kortsluitvastheid van HCMOS-uitgangen is betrekkelijk. Bij voldoende voedingsspanning kan de kortsluitstroom een dusdanige waarde bereiken dat de interne dissipatie kritisch wordt. Kortstondige kortsluitingen blijken in de praktijk probleemloos overleefd te worden.

De 4000-serie gedraagt zich beduidend minder pittig dan de HC- en HCT-serie. Bij 5 V is de uitgangskortsluitstroom 5 mA typ., bij 10 V geldt een waarde van ongeveer 25 mA.

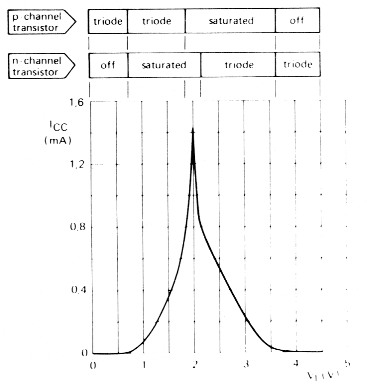

Ontkoppelen

De HF-ontkoppeling van voedingslijnen is een vaak onderschatte noodzaak. Hoewel het (statisch) stroomverbruik van CMOS geringer is dan dat van bipolaire TTL, is de noodzaak van ontkoppeling bij CMOS groter. Bij het omschakelen trekt een CMOS-poort kortstondig een "grote" stroom (figuur 9). Op dat moment zijn beide komplementaire uitgangstransistors in geleiding. Het dynamisch stroomverbruik, de voedingsstroomvariaties ten gevolge van het schakelen, is derhalve relatief groot. CMOS moet daarom krachtiger ontkoppeld worden dan bipolaire TTL; laat u niet door het lagere statische stroomverbruik om de tuin leiden. Aan de andere kant heeft CMOS, voor zover we het niet over de TTLkompatibele variant hebben, een grotere storingsmarge vanwege de symmetrische schakelnivo's. CMOS en HCMOS is daarom toleranter ten aanzien van spikes op de voeding ten opzichte van (LS)TTL en HCT-MOS.

Figuur 9. Het stroomverbruik van CMOS is een funktie van de momentele ingangsspanning.

Tabel 1

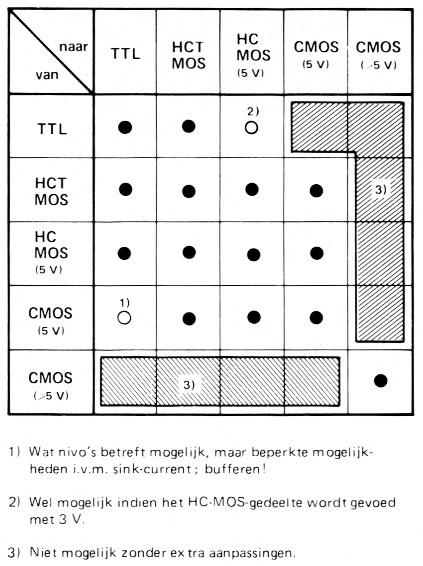

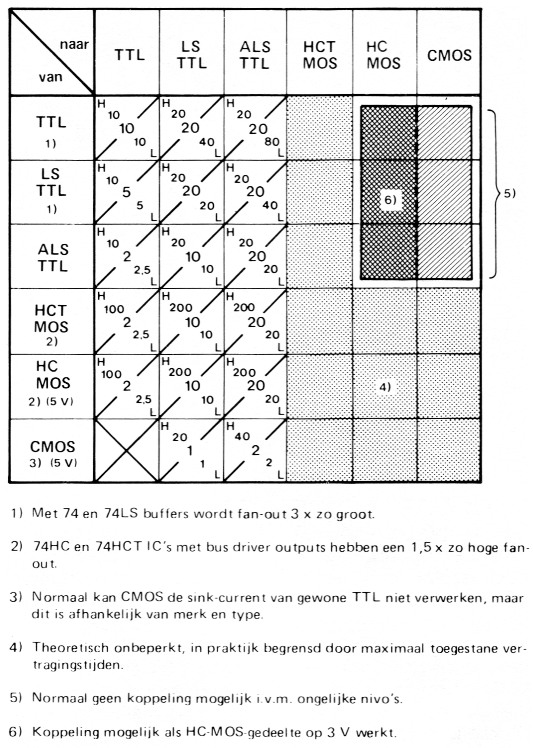

Koppelen van families

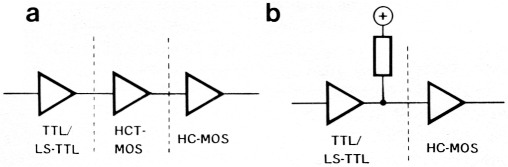

In de praktijk zullen veelvuldig verschillende logische families gekoppeld moeten worden. Uitgaande van het gegeven dat voor een gelijke voedingsspanning wordt gekozen, zijn er in hoofdzaak twee beperkende faktoren: het beperkte logisch-1-nivo dat (LS)TTL kan leveren en de noodzakelijke sink-stroom om een (LS)TTL-ingang laag te maken.

Wordt CMOS aangestuurd met TTL, dan kan dat door voor HCT te kiezen of door het TTL-hoog-nivo op te krikken met een pull-up-weerstand (figuur 10b). Zonder zo'n pull-up-weerstand zal HCMOS als gevolg van het te lage ingangsnivo beduidend meer stroom vragen (figuur 9) en in het meest extreme geval, als een TTL-uitgang maar net 2,4 V levert, zou dit niet eens als een een geinterpreteerd worden. Vanuit HCT kan vervolgens zonder probleem "normale" CMOS (74HC- of 4000-serie) aangestuurd worden. De HCT-uitgangskonfiguratie is immers exakt dezelfde als die van HC. Tussen een TTL-(kompatibele-)uitgang en (H)CMOS moet zich dus minstens een HCT-poort bevinden (figuur 10a).

Figuur 10. Bij aansturing van CMOS vanuit TTL(kompatibele)-logica moet voor een voldoende hoog "1"- nivo gezorgd worden.

TTL aansturen vanuit HC of HCT is zonder meer mogelijk, maar voor niet-LS-TTL geldt wel een beperkte fan out.

De 4000-serie CMOS is niet in staat gewone TTL aan te sturen, maar bij LSTTL lukt het net met een fan out van 1.

In tabel 2 is een overzicht van de koppelmogelijkheden gegeven. De fan out wordt in deze tabel voor zowel een logische 1 als een logische O gegeven. De laagste van deze twee fan outs is de nog praktisch bruikbare.

Tabel 2

Ongebufferde logica

CMOS-logica is tegenwoordig in de regel gebufferd, hoewel er binnen elke serie nog wel enkele poortjes in ongebufferde uitvoering leverbaar zijn (74HCUO4 en 4049UB bijvoorbeeld waarbij de "U" in de typeaanduiding "unbuffered" indiceert).

Het is niet zo dat gebufferde IC's per definitie meer uitgangsstroom kunnen leveren. De essentie van buffering is dat aan de uitgang de spanning onafhankelijk is van de ingangsspanning en aan de ingang dat het schakelnivo van de ene ingang niet beinvloed wordt door de spanning op een andere ingang. Buffering houdt dus ontkoppeling van ingangen en uitgangen onderling in. In feite is de spanningsversterking opgevoerd dankzij een extra trap (het omkaderde gedeelte in figuur 7).

Vanwege de lagere spanningsversterking van ongebufferde logica, is het eenvoudiger deze in het lineaire gebied te gebruiken.

Onheuse monoflops

We maken een uitstapje naar het tijddomein. In (asynchrone) logische schakelingen zijn nogal eens delays of gedefinieerde pulsen nodig. Een monoflop is daartoe het geëigende middel en alle logische families omvatten dan ook minstens een zo'n monoflop-IC. De puls- of vertragingstijd kan simpel met een RC-tak ingesteld worden.

De met printoppervlakte woekerende ontwerper heeft echter vaak helemaal geen zin om voor zoiets triviaals als een pulsje een extra IC uit de kast te trekken. Hij grijpt naar een RC-takje en smeedt dit met een toevallig overgebleven poortje samen tot een kwasi-monoflop. Dit is een legitieme methode, zij het dat er beperkingen zijn.

De eerste beperking is dat de ingangspuls langer moet zijn dan de gewenste uitgangspuls. Dit type monoflop werkt dus alleen als pulsverkorter, niet als pulsverlenger.

De tweede komplikatie wordt gevormd door beïnvloeding van de monoflop-tijd door de ingangsstroom. Bij CMOS (4000-, 74HC- en 74HCT-serie) is deze verwaarloosbaar klein. Dat betekent dat bij deze logica-series monoflops volgens dit model zonder principiële beperkingen aan de weerstandswaarde gerealiseerd kunnen worden.

De lengte van de uitgangspuls wordt mede bepaald door het ingangsschakelnivo. Omdat bij 74HC- en 4000-logica dit nivo halverwege de voedingsspanning ligt, zal bij gelijke dimensionering de schakeling van lia een even lange puls opleveren als die van 11b. Bij 74HCT zal de puls van 11a langer zijn dan die van 11b.

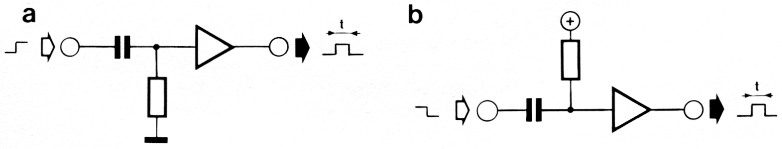

Figuur 11. Monoflops met normale poorten.

Kwasi-monoflops in (LS)TTLtechnologie zijn problematischer. In geval van figuur lia moet de weerstand kleiner dan 1k4 gekozen worden om de ingangsstroom zonder al te veel spanningsverlies te verwerken. Om tot praktisch bruikbare uitgangspulsen te komen moet de kondensator nu relatief groot gekozen worden. Daar komt bij dat het aansturen van deze monoflop vanuit een TTLuitgang maar nauwelijks mogelijk is omdat deze uitgang slechts een zeer beperkte source-stroom kan leveren.

11 b biedt betere perspektieven voor een TTLmonoflop. De weerstand kan veel hoger gekozen worden maar de uiteindelijke monofloptijd zal niet zo zeer door deze weerstand, doch veel meer door de ingangsstroom en natuurlijk de waarde van de kondensator bepaald worden. Het maken van delays is mogelijk door de R en de C in figuur 11 van plaats te verwisselen. Ook nu geldt dat bij TTL de weerstand kleiner dan 1 k4 gekozen moet worden, hetgeen tot weinig bruikbare oplossingen leidt. Bij CMOS zijn er geen beperkingen.

Oscillatoren

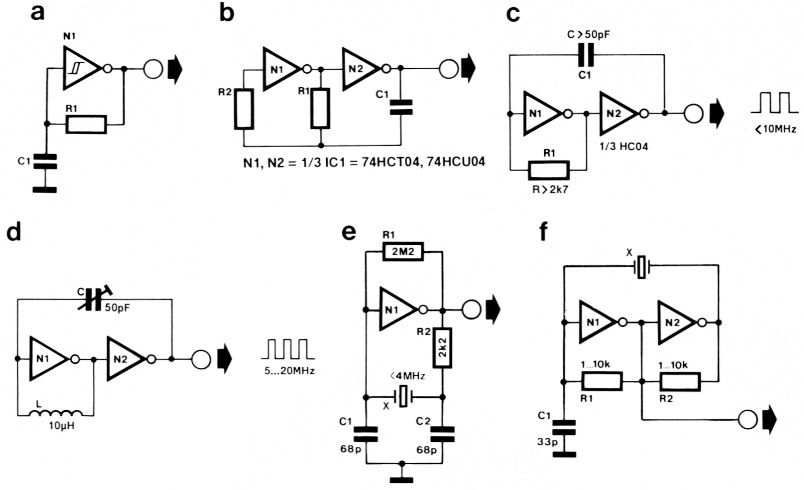

Van monoflop naar astabiele is maar een kleine stap. 12a toont de eenvoudigste RC-oscillator met een Schmitt-trigger/inverter. De frekwentie is afhankelijk van de schakelnivo's. Men moet er rekening mee houden dat deze per fabrikaat verschillen en vaak ook een behoorlijke (voedingsspaningsafhankelijke) tolerantie hebben. Echt reproduceerbare frekwenties zijn met deze oscillator daarom moeilijk te verkrijgen.

De tweede variant, een RC-oscillator met twee inverters, geeft een veel reproduceerbaardere frekwentie (12b) die hoofdzakelijk bepaald wordt door R1 en C1, onder voorwaarde dat R2 relatief groot gekozen wordt t.o.v. R1 (faktor 2 . . . 10 groter). Deze frekwentie is bovendien redelijk voedingsspanningsonafhankelijk. Als inverters kunnen ook NOR's of NAND's gebruikt worden. Als inverter geschakelde EXOR's moeten we afraden, omdat deze zullen jitteren bij het omschakelen. Nummer drie in de rij is een variant op de voorgaande, waarbij feitelijk R2 gereduceerd is tot O Ω. Met deze oscillator zijn wat hogere frekwenties mogelijk, maar er staat een grotere afhankelijkheid van de voedingsspanning tegenover. Voor nog hogere frekwenties (tot 2 MHz) kan de weerstand door een spoel vervangen worden (12d).

Figuur 12. Een oscillator-parade.

In 12e zien we een zogenaamde Pierce-oscillator, die een door een kwartskristal gestabiliseerde frekwentie levert. R2 moet oversturing van het kristal voorkomen als gevolg van de (te) lage uitgangsimpedantie van HCMOS. Omdat deze weerstand voor extra fasedraaiing zorgt, wordt de volgens dit koncept maximaal haalbare frekwentie beperkt tot 4 MHz. 12f toont weer een ander veel gebruikt oscillatorrecept. Zowel met TTL-LS als met HCMOS funktioneert dit type. Bij gebruik van HCMOS moeten volgens de overlevering HCUpoorten gebruikt worden, maar in Elektuur hebben we al eerder met sukses met gewone HCT een dergelijke oscillator toegepast. Gezien de uitgebreidheid en het specialisme van het onderwerp, zullen we binnenkort in Elektuur in een apart artikel uitgebreider ingaan op kristaloscillatoren met logische poorten.

Logische VCO

Het maken van een oscillator is ook mogelijk door een oneven aantal inverters in serie te schakelen en terug te koppelen. In dit geval wordt van de poortvertragingstijden gebruik gemaakt. Het is nu juist wel belangrijk dat gebufferde poorten gebruikt worden. Omdat die poort-vertragingstijd bij (H)CMOS afhankelijk is van de voedingsspanning, kan hiermee de frekwentie redelijk lineair gestuurd worden. Aan de schakeling van figuur 13 is N5 als versterker-trap toegevoegd om een konstante uitgangsamplitude te krijgen, onafhankelijk van de voedingsspanning van N1 ... N4.

Figuur 13. Door gebruik te maken van de spanningsafhankelijke poortvertragingstijd van HCMOS kan een VCO gemaakt worden.

Sinus-oscillator

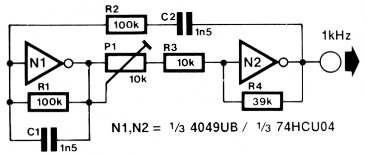

Op de titel "meest analoge digitale schakeling" in dit relaas kan de sinusgenerator van figuur 14 aanspraak maken. Feitelijk is dit een Wienbrug-oscillator die, onder voorwaarde dat R1 = R2 = R en C1 = C2 = C, werkt op de frekwentie 1/2πRC. Met de gegeven dimensionering komen we dus op ongeveer 1 kHz uit.

De verzwakking van de eerste trap rond N1 moet gekompenseerd worden door de als inverterende versterker geschakelde trap rond N2. De versterking R4/(R3+P1) moet nauwkeurig afgestemd worden, zodat de totale rondgaande versterking precies een wordt. Bij te veel versterking zal de uitgang vastlopen tegen de voeding met uiteraard de nodige vervorming en bij te weinig versterking slaat de oscillator af.

In principe is het zelfs mogelijk om een op frekwentie instelbare sinusgenerator te maken door R1 en R2 te vervangen door een stereopotmeter (2 × 100 k) met in elke sektie bijvoorbeeld 10 k in serie. In de praktijk blijkt deze oplossing wel te werken, maar ideaal is anders. Afhankelijk van de stand van de stereo-potmeter zou, voor een minimale vervorming, de versterking met P1 "getuned" moeten worden. Dat aanpassen van de versterking is ook nodig bij veranderen van de voedingsspanning omdat de open-lus-versterking van N1 en N2 spanningsafhankelijk is.

Figuur 14. Twee als lineaire versterker geschakelde inverters vormen hier een RC-sinus-oscillator.

Literatuur

- Philips high speed CMOS designer guide, January 1986

- Logische familieaangelegenheden, Elektuur maart 1984

- Sinewave oscillator using CMOS inverters, Electronics & Wireless World, february 1988

- diverse databoeken TTL, CMOS, HCMOS