Buffermos, verschillen en overeenkomsten tussen gebufferde en ongebufferde CMOS

Digitale CMOS-IC's zijn verkrijgbaar in twee 'soorten', namelijk in ongebufferde en gebufferde uitvoering. De bedoeling van dit artikel is, zonder dat er wordt ingegaan op de fabrikagemetode die vaak per fabrikant anders is, duidelijk te maken waar de essentiële verschillen liggen en onder welke omstandigheden de voorkeur gegeven moet worden aan ongebufferde CMOS dan wel 'buffermos'.

Voor de elektronica-amateur zijn er twee families van logische IC's in hoofdzaak van belang: TTL en CMOS. TTL, een afkorting van TransistorTransistor-Logic, is een zg. bipolaire techniek. Van bipolaire technieken spreekt men wanneer er gebruik gemaakt wordt van twee soorten halfgeleidermateriaal (P- en N-materiaal, in de regel silicium), die aan elkaar gelegeerd worden en een kontaktvlak of junction opleveren waardoor een stroom vloeit. De gewone transistor is het bekendste voorbeeld van een bipolaire halfgeleiderkomponent. De naam TTL is ontleend aan de wijze waarop de in de IC's ondergebrachte transistoren onderling gekoppeld zijn tot logische schakelingen.

De TTL-familie kent een onderverdeling. Zo is er behalve de standaard-uitvoering ook nog Low Power Schottky TTL (afgekort LS-TTL), High Speed TTL (H-TTL) en nog drie andere uitvoeringen. De LS-variant is sterk in opkomst en zal naar verwachting binnenkort standaard-TTL van de eerste plaats verdringen. Een andere familie van bipolaire logica is bije. ECL (Emitter Coupled Logic). CMOS is een variant van de MOS-technologie. MOS staat voor Metal Oxide Semiconductor. In de MOS-techniek maakt men gebruik van veldeffekttransistoren of FET's (Field Effect Transistor), d.w.z. unipolaire transistoren waarbij door de grenslagen van het P- en N-materiaal geen (of altans nauwelijks) stroom loopt, maar wel langs de grenslagen, evenwijdig daaraan. De MOSFET is een speciale uitvoering van de FET waarbij door het toepassen van een extra laagje isolerend siliciumoxide tussen het P- en het N-materiaal de invloed van de toch al uiterst kleine stroom door de grenslaag nog eens tot een minimum is beperkt.

De MOS-familie

De MOS-familie kent verschillende soorten IC's, al naar gelang welke technieken er zijn gebruikt om de logische funktie op.te bouwen. Net zoals er PNP- en NPN-transistoren bestaan, is het ook mogelijk N-kanaalsFET's en P-kanaals-FET's te konstrueren. Worden er uitsluitend N-FET's gebruikt, dan spreekt men van N-MOS, bij toepassing van uitsluitend P-FET's van P-MOS en bij toepassing van zowel N- als P-FET's van CMOS (C staat hier voor Complementary). CMOS is verkrijgbaar in twee uitvoeringen: ongebufferd en gebufferd. De laatstgenoemde heet in het jargon ook wel kortweg buffermos. Beide soorten worden door verscheidene fabrikanten op de markt gebracht en moeten sinds enige tijd voldoen aan bepaalde minimum-specifikaties die zijn vastgelegd in de zg. JEDEC-norm van het Amerikaanse EIA-instituut. Door deze norm is de onderlinge uitwisselbaarheid van de IC's van verschillende fabrikanten gewaarborgd.

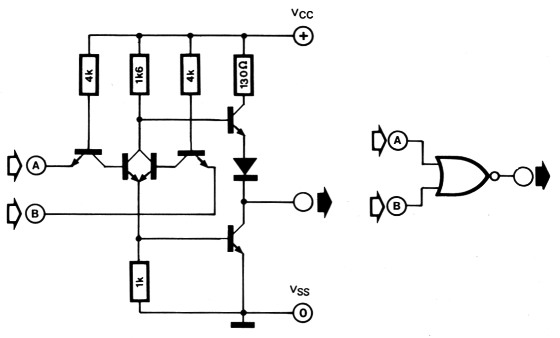

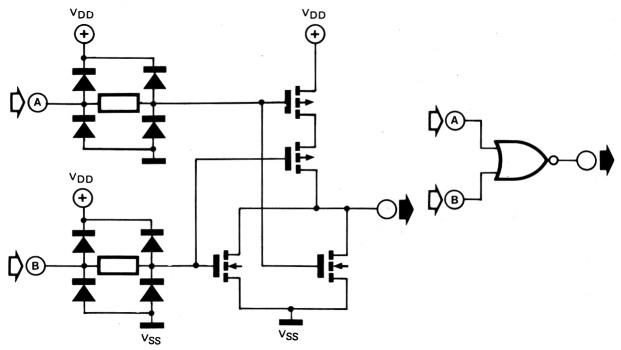

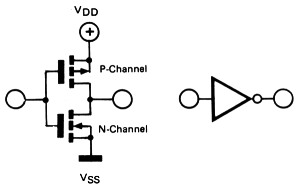

In figuur 1a en 1b zijn ter vergelijking een TTL-NOR-poort en een CMOS-NOR-poort getekend. In de CMOS-schakeling is VDD een positieve spanning, terwijl VSS in de regel aan aarde ligt. Het logische nivo '1' komt overeen met VDD en logische '0' met VSS. Bij de CMOS-schakeling valt direkt op, dat er vanwege de komplementaire FET's geen weerstanden nodig zijn en dat de gehele schakeling uit slechts vier FET's bestaat. De dioden en de weerstand die toch in figuur 1b zijn toegevoegd, dienen uitsluitend ter bescherming van de ingang tegen te hoge spanningen en zijn niet noodzakelijk voor het tot stand brengen van de logische funktie. Hoe een en ander werkt kan worden verduidelijkt aan de hand van figuur 2, waar de meest eenvoudige logische schakeling, een inerter, is getekend. Deze inerter bestaat uit slechts twee FET's, een N- en een P-type. Staat er een logische '1' aan de ingang, m.a.w. ligt de ingang aan VDD, dan spert de P-FET en geleidt de N-FET. De uitgangsspanning is dus gelijk aan VSS, logisch '0'. Een '0' aan de ingang veroorzaakt een omgekeerd effekt: de P-FET geleidt en de N-FET spert, waardoor er een '1' verschijnt op de uitgang.

Figuur 1. De inwendige schema's van een NOR-poort zoals die gerealiseerd wordt in TTL (1a), ongebufferde CMOS (1b) en gebufferde CMOS (1c).

Duidelijk is, dat op deze wijze de beide FET's nooit gelijktijdig geleiden (afgezien van een zeer kort moment tijdens het omschakelen) en dat de inverter zelf daardoor geen energie verbruikt.

In de praktische schakeling is er altijd een zekere kapaciteit aan de uitgang (in het algemeen bedradingskapaciteit, in de grootte-orde van enkele tientallen pF's) en deze kapaciteit moet steeds worden geladen en ontladen als de uitgang '1' resp. '0' wordt. Deze stroom wordt aan de voeding onttrokken. Het stroomverbruik van een CMOS-poort neemt dan ook evenredig toe met de frekwentie. Ook het vermogensverlies (dissipatie) in het IC neemt toe, want hoewel er geen weerstanden in voorkomen, zijn de beide FET's helaas geen ideale schakelaars en hebben als ze geleiden een ohmse weerstand van ongeveer 400 Ω.

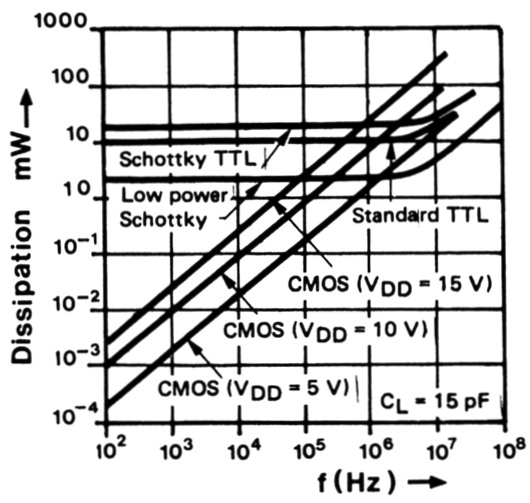

Algemeen mag worden gesteld, dat CMOS zeer weinig vermogen opneemt bij lage frekwenties. Voor hoge frekwenties is de dissipatie echter nog groter dan die van TTL, zoals duidelijk blijkt uit figuur 3, waar een vergelijking wordt gemaakt tussen de dissipaties van standaard- en LS-TTL enerzijds, en CMOS bij drie verschillende voedingsspanningen anderzijds.

De NOR-funktie ziet er wat ingewikkelder uit dan de inverter (figuur 1 b). De werking is eenvoudig te begrijpen, als men zich realiseert dat zodra een van de beide ingangen '1' is, er een laagohmige verbinding tussen uitgang en VSS ontstaat omdat er een N-FET gaat geleiden, terwijl de bijbehorende P-FET spert. (NB: in tegenstelling tot bij NPN-transistoren wordt de N-FET aangegeven met het pijltje 'naar binnen' gericht.) De beide P-FET's staan in serie en de verbinding tussen VDD en de uitgang blijft dus hoogohmig. Pas wanneer alle ingangen '0' zijn, gaat de serieschakeling van de P-FET's geleiden en spert de parallelschakeling van de N-FET's. En dit komt precies overeen met de NOR-funktie.

Gebufferde MOS

Sinds enkele jaren is gebufferde CMOS verkrijgbaar. Het ziet er zelfs naar uit, dat het grootste markt-aandeel wordt ingenomen door-gebufferde CMOS. Buffermos heeft dus kennelijk een aantal voordelen. Deze ontwikkeling verdient enige aandacht, want het is beslist niet altijd zo, dat gebufferde en ongebufferde IC's in een bestaande schakeling zonder meer zouden kunnen worden uitgewisseld. In een groot aantal gevallen, zoals in schakelingen die relatief langzaam zijn, waarvan de timing niet erg belangrijk is en waarin geen slechte flanken voorkomen, zal gebufferde CMOS net zo goed funktioneren, maar algemeen geldt dit zeker niet. Dit zal duidelijker zijn na onderstaande uitleg.

Gebufferde CMOS onderscheidt zich van 'gewone' CMOS op twee punten: de uitgangsimpedantie is konstant (dit is bereikt door toevoeging van een 'buffer', een extra trap dus) en door een wat grotere storingsongevoeligheid. Verder zijn de minimum-specifikaties voor beide soorten gelijk.

In figuur 1c is het schema van een gebufferde NOR in CMOS-techniek weergegeven. Direkt valt het veel grotere aantal komponenten op, dat gelukkig geen konsekwenties heeft voor de prijs van de IC's, omdat alle FET's in een proces gelijktijdig worden vervaardigd. De symbolische weergave van de funktie naast het schema helpt de schakeling te doorzien: De ingangen A en B worden eerst geïnverteerd (twee maal een inverter schakeling zoals in figuur 2), dan volgt een NAND en dan nog eens een inverter. Deze schakeling geeft in zijn geheel de NOR-funktie. Het was overigens ook mogelijk geweest om, zoals in het bovenste symbolenschema is aangegeven, de NOR-funktie te handhaven en de buffering te bereiken door achter de NOR twee inverters te plaatsen (een aantal fabrikanten doet dit ook).

Figuur 2. De meest elementaire schakeling in de CMOS-techniek, de inverter. Afhankelijk van de logische toestand is een van de beide MOSFET's in geleiding terwijl de andere spert.

Figuur 3. Het opgenomen vermogen van standaard-TTL, Low Power Schottky TTL en CMOS bij verschillende voedingsspanningen per poortschakeling, en zoals dat varieert met de frekwentie van het logische ingangssignaal. Duidelijk is te zien dat de dissipatie bij CMOS sterk toeneemt bij het hoger worden van de frekwentie en dat deze bij hoge frekwenties zelfs groter is dan die van de beide TTLsoorten.

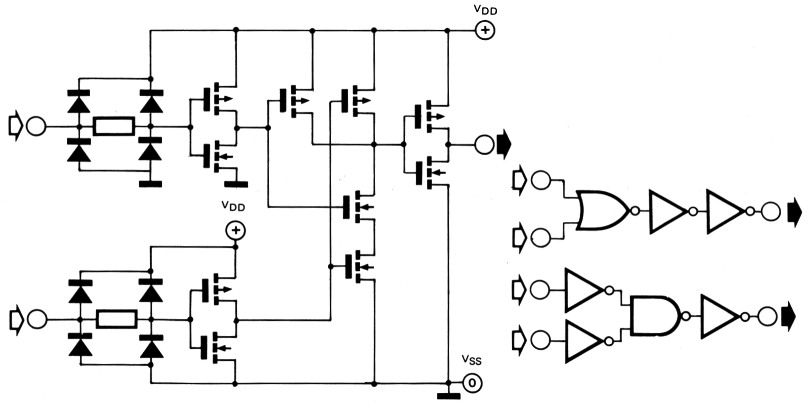

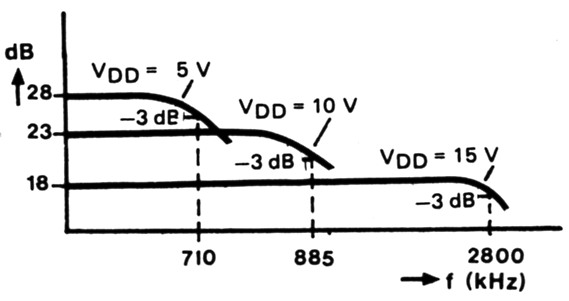

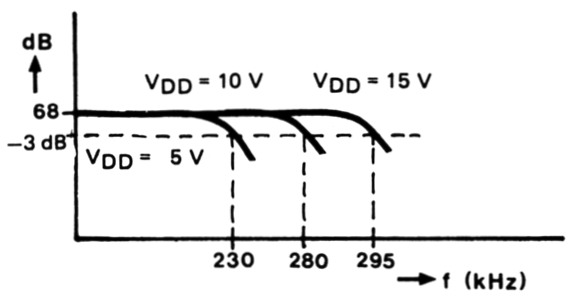

Zo op het eerste gezicht is het duidelijk, dat omdat de gebufferde versie twee trappen extra bezit, de vertraging van in-naar uitgang veel groter zal zijn dan bij de ongebufferde versie. Ook de versterking zal aanzienlijk groter zijn. Met name de toegenomen versterking beïnvloedt de eigenschappen aanzienlijk (zie ook figuur 4).

Figuur 4. De versterking van een CMOSpoortschakeling bij ongebufferde (4a) en gebufferde (4b) uitvoering, en bij drie verschillende voedingsspanningen. De versterking van de van buffers voorziene CMOS-poort is bij alle voedingsspanningen aanzienlijk groter dan die van de ongebufferde poort. Bovendien is de versterking onafhankelijk van de voedingsspanning.

Uitgangsimpedantie

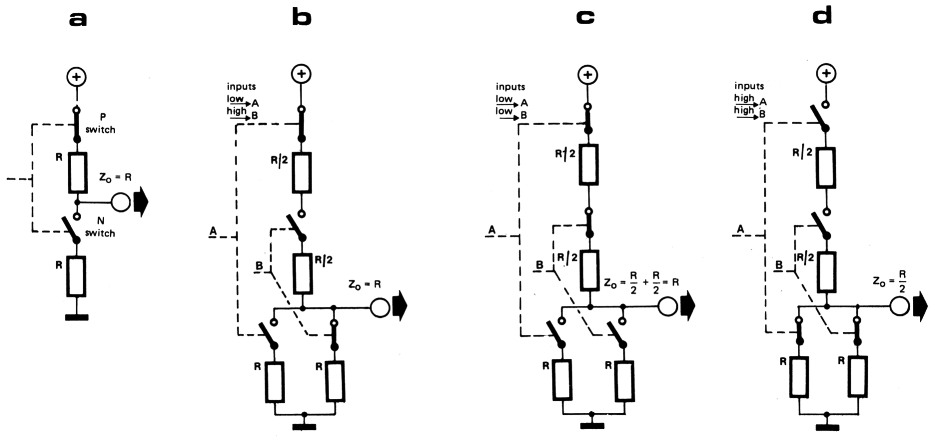

Een van de voordelen die buffermos biedt ten opzichte van ongebufferde CMOS is het feit dat de eerstgenoemde familie een konstante, van het uitgangsnivo onafhankelijke uitgangsimpedantie heeft. Ter toelichting daarvan dient figuur 5.

Figuur 5. Vereenvoudigde weergave van de werking van een CMOS-inverter (5a). De beide FET's worden voorgesteld als een serieschakeling van een schakelaar en een weerstand R. Van de inverter is altijd een schakelaar open en een gesloten. Men ziet dat de uitgangsimpedantie Zo altijd gelijk is aan R. De figuren 5b ... d tonen een op dezelfde wijze vereenvoudigde voorstelling van de werking van een ongebufferde CMOS-NORpoort. Te zien is dat de uitgangsimpedantie van deze schakeling varieert tussen R en 1/2 R.

In figuur 5b ... d is de werking van de ongebufferde NOR-poort weergegeven. Elke FET is voorgesteld door de (kleine) doorlaatweerstand en een schakelaar. Als de FET spert moet men zich voorstellen dat de overeenkomende schakelaar open is; geleidt de FET dan is de schakelaar gesloten. Het is nu in de figuur te zien dat de uitgangsimpedantie ZO gelijk is aan ½ R wanneer de beide poortingangen hoog zijn, en gelijk aan R wanneer een of beide ingangen aan een laag nivo liggen. Bij poortschakelingen met meer dan twee ingangen wordt de variatie in uitgangsimpedantie bij veranderend uitgangsnivo nog groter. Figuur 5a toont een vervangingsschema van het uitgangscircuit van een gebufferde CMOS-schakeling. Ook hier is weer iedere FET voorgesteld als serieschakeling van een weerstand R en een schakelaar. Aangezien van de beide schakelaars er altijd een open is en een dicht, is de uitgangsimpedantie van deze uitgangsbuffer, en dus van de buffermos-schakeling, altijd gelijk aan R. Het voordeel van een van het uitgangsnivo onafhankelijke uitgangsimpedantie is dat de flanksteilheid van op- en neergaande flank aan elkaar gelijk zijn.

Versterking

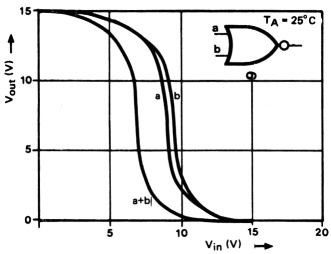

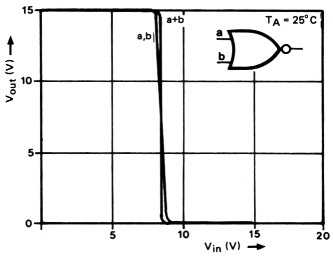

Een ander kenmerk waardoor buffermos zich onderscheidt van ongebufferde CMOS is de grotere versterking (zie figuur 4). Door deze grotere versterking is de overdrachtkarakteristiek tussen in-en uitgang veel rechthoekiger (figuur 6). Bovendien maakt het niet meer uit of slechts een dan wel meerdere ingangen worden gestuurd. Bij de gebufferde uitvoering wordt een spanning van bijv. 7 volt nog duidelijk als logisch 'nul' herkend (bij een voedingsspanning van 15 V), terwijl de ongebufferde versie bij sturing van beide ingangen dit reeds als een '1' ziet. De marge, waarbinnen de ingangssignalen mogen liggen, wordt voor de gebufferde uitvoering dan ook aangegeven met 0-30% van de voedingsspanning, terwijl deze voor de ongebufferde versie 0-20% bedraagt. Als nadeel staat hier tegenover, dat wanneer het ingangssignaal te langzaam verandert en binnen 30-40% ligt, er door de grotere versterking oscillaties kunnen ontstaan.

Figuur 6. Spanningsoverdrachtkarakteristiek van zowel een ongebufferde als een gebufferde CMOS-NOR-poort. Die van de gebufferde poort is veel rechthoekiger. Bovendien maakt het bij de gebufferde uitvoering nauwelijks verschil of er slechts ddn (kurve a of b) of beide (a + b) ingangen worden gebruikt.

Samenvattend

In tabel 1 zijn de waarden van enkele parameters voor zowel gebufferde als ongebufferde CMOS met elkaar vergeleken (naar gegevens van RCA). Zetten we de verschillende voordelen voor de beide CMOS-families nog eens or een rijtje.

| gebufferd | ongebufferd | ||

|---|---|---|---|

| vertragingstijd | 150 | 80 | ns |

| noise immunity | 30 | 20 | % |

| noise margin | 1 | 0,5 | V |

| uitgangsimpedantie (poort met vier ingangen) | 400 | 100...400 | Ω |

| transition time | 100 | 60 ... 100 | ns |

| wisselspanningsversterking | 68 | 23 | dB |

| bandbreedte | 280 | 885 | kHz |

| optreden van oscillatie aan uitgang (experimenteel bepaald) | kan optreden bij stijgtijden ≥ 1 ms | niet waarneembaar bij stijgtijden ≤ 100 ms | |

| ingangskapaciteit | |||

| gemiddeld | 1 ... 2 | 2 ... 3 | pF |

| maximaal | 2 ... 4 | 5 ... 10 | pF |

Gemeten bij een voedingsspanning van 5 V; CL = 50 pF

Gebufferde CMOS heeft als voordelen:

- betere storingsmarge

- konstante uitgangsimpedantie

- lagere ingangskapaciteit

Ongebufferde CMOS biedt de volgende voordelen:

- kortere vertragingstijd

- lagere gevoeligheid voor de stijgtijd van het ingangssignaal

CMOS-TTL-CMOS

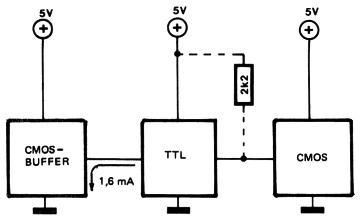

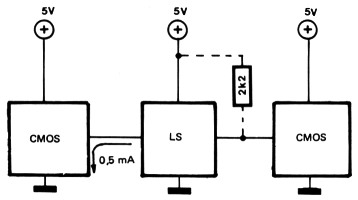

Het komt wel eens voor, dat er zowel TTL als CMOS wordt gebruikt in een schakeling. Alle CMOS IC's die aan de JEDEC-norm voldoen, kunnen direkt een Low Power Schottky TTL poort met een fan-in van 1 aansturen. Om standaard-TTL aan te sturen is het noodzakelijk een buffer (zoals de 4049 of de 4050) op te nemen, aangezien er in dit geval een stroom moet kunnen vloeien van tenminste 1,6 mA en de CMOS-uitgang maar 0,5 mA kan verwerken.

Wordt CMOS aangestuurd vanuit TTL, dan kan dit direkt gebeuren. De stoorafstand kan desgewenst worden verbeterd door een weerstand van enkele kSt op te nemen, zoals is aangegeven in figuur 7.

Figuur 7. De aanpassing tussen al dan niet gebufferde CMOS en standaard-TTL (7a) en Low Power Schottky (7b). Rechtstreekse sturing van TTL is alleen mogelijk vanuit gebufferde CMOS; Low Power Schottky TTL kan ook vanuit ongebufferde CMOS worden gestuurd. De weerstand van 2k2 is niet noodzakelijk, maar verbetert het schakelgedrag.

Typenherkenning

Door de komst van het gebufferde CMOS volstaat het niet meer het typenummer te herkennen. Het moet bovendien duidelijk zijn of het een gebufferde of ongebufferde versie betreft. In principe is het zo, dat gebufferde uitvoeringen 'B' achter het typenummer, en ongebufferde uitvoeringen 'UB' achter het typenummer krijgen. Helaas houden lang niet alle fabrikanten zich hieraan. De IC's, die zijn voorzien van 'B' of 'UB' moeten voldoen aan de JEDEC-specs volgens tabel 2. Niet alle fabrikanten echter garanderen hun IC's voor een voedingsspanning van 18 volt. Zo is er bijv. de veel gebruikte serie met het achtervoegsel 'A', die kwa eigenschappen in de ongebufferde kategorie thuishoort maar slechts gegarandeerd is tot 15 volt. Een zeer geschikte reeks, mits er rekening wordt gehouden met de iets lagere maximale voedingsspanning. Door Elektuur wordt gewoonlijk de 4000-serie gebruikt, die onder dezelfde nummers door meerdere fabrikanten wordt gemaakt. Nagenoeg alle fabrikanten verlenen echter (helaas!) een 'persoonlijk tintje' aan hun IC's door de kodering met letters of kombinaties daarvan uit te breiden. Bovendien wordt de herkenning van een bepaald IC vaak bemoeilijkt omdat er meestal niet de naam, maar een of ander vignet van de fabrikant op is gestempeld. De ongeoefende waarnemer zal dit in het algemeen niet herkennen. Een hulp hierbij zijn de foto's van enkele IC's die hier staan afgedrukt.

| Absolute Maximum Ratings (Voltages referenced to VSS): | |

|---|---|

| DC Supply Voltage VDD | -0.5 to +18 V |

| Input Voltage Vin | -0.5 to VDD +0.5 V |

| DC Input Current (any one input) Iin | ±10 mA |

| Storage Temperature Range | -65 to +150 °C |

| Total dissipation | 400 mW |

| Recommended Operating Conditions: | |

| DC Supply Voltage VDD | +3 to +15 V |

| Operating-Temperature Range: | |

| Military-Range Devices | -55 to +125 °C |

| Commercial-Range Devices | -40 to +85 °C |

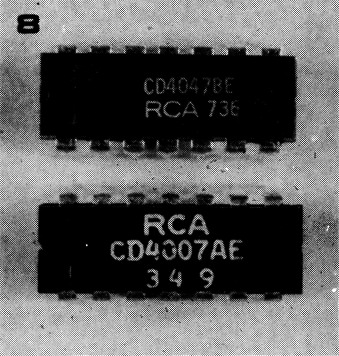

Figuur 8. RCA levert verschillende reeksen CMOS, dat bij deze fabrikant overigens COSMOS heet. Van alle reeksen wordt het typenummer voorafgegaan door de letters CD. Na de vier cijfers (het 4000-nummer) volgen nog een aantal letters. De laatste letter geeft de behuizing van het IC aan: een E duidt op een plastic behuizing, een D op een keramische. Deze laatste letter wordt voorafgegaan door een A (niet gebufferd, maximum voedingsspanning 15 V), de letters UB (niet gebufferd, 18V) of een B (gebufferd, 18V).

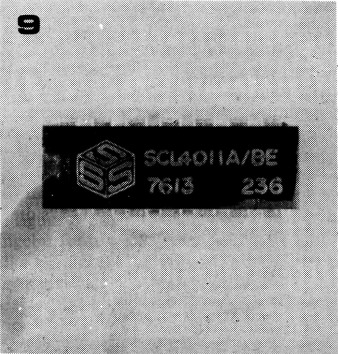

Figuur 9. Solid State Scientific laat zijn typenummers voorafgegaan door de letters SCL (altans voor de goedkopere IC's). De vier cijfers worden gevolgd door letters, waarvan de laatste, evenals bij RCA, in geval van een plastic behuizing een E is, en in geval van een keramische een D. Deze laatste letter wordt bij de oudere Solid State Scientific IC's voorafgegaan door een A (ongebufferd) of de aanduiding A/B (gebufferd). Bij IC's die na 1976 zijn geproduceerd zijn de aanduidingen voor ongebufferd en gebufferd respektievelijk UB en B. Alle IC's van Solid State Scientific zijn gegarandeerd voor een voedingsspanning van tenminste 18 V. Overigens kan men aan de hand van de vier cijfers de IC's ook nog in drie groepen onderverdelen: de 4000-reeks van RCA-standaardfunkties, de 4500-reeks van Motorola-standaardfunkties en de 4400-reeks van meer gespecialeerde, op specifieke toepassingen gerichte IC's. SSS-IC's zijn voorzien van een produktiedatum (1976, 13e week) en een volgnummer (236) die de serie uit die periode aangeeft.

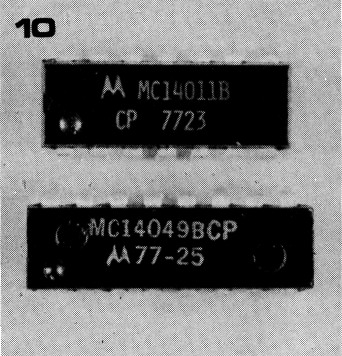

Figuur 10. Motorola noemt zijn CMOSprogramma McMOS. De soort behuizing wordt aangeduid met P (plastic) en L (keramisch). Verder komt er een C (commercial) voor op de standaard IC's (tot 16 volt bruikbaar) en een A op de betere typen (18 volt, groter temp. bereik). Tegenwoordig wordt direkt achter de cijfers nog de kode B of UB gegeven, deze IC's voldoen aan de JEDEC-norm.

Bij Motorola wordt het typenummer voorafgegaan door een M en een 1. De 14000-serie komt overeen met de 4000-serie. De 14500-serie is een reeks IC's naar oorspronkelijk Motorola ontwerp. De 14400- serie wijkt in zijn specifikaties af van standaard-McMOS; het betreft zeer specifieke IC's zoals horloge-IC's e.d.

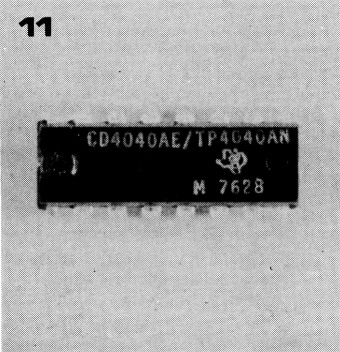

Figuur 11. Texas Instruments bezigt als vignet een gestileerde kontour van de Amerikaanse staat Texas. Deze fabrikant noemt zijn CMOSreeks TiCMOS en laat het typenummer voorafgaan door zowel CD als TP. Er is zowel een ongebufferde A-serie als een gebufferde B-serie.

Figuur 12. National Semiconductor hanteert twee verschillende fabrieksvignetten, die overigens niet duiden op enig technisch verschil: de IC's met het ene vignet zijn volledig uitwisselbaar met die met het andere. Alle typeaanduidingen van National's CMOSIC's beginnen met de letters CD. Na de vier cijfers komt weer een letterkombinatie. De op een na laatste letter daarvan refereert aan het temperatuurgebied waarin de werking van het IC gegarandeerd wordt IC voor het standaard temperatuurgebied, M voor het uitgebreide) en de laatste letter aan de behuizing (N voor plastic, D of J voor keramisch). Volgens JE DEC levert National gebufferde (B) en ongebufferde (UB) CMOS voor 18 volt. De oude (15 V) ongebufferde CMOS heeft geen extra aanduiding. Alle soorten worden aanbevolen voor voedingsspanningen tot 15 V. National fabriceert ook CMOS-varianten van de TTL-IC's uit de bekende 7400-serie. Deze IC's realiseren dezelfde logische funkties als die van de TTL-reeks en zijn er ook mee pin-kompatibel. De nummering die National gebruikt om deze CMOS-IC's aan te duiden is MM74C .. N (voor plastic behuizing) of MM74C .. J (keramisch), waarbij de twee stippen staan voor de laatste twee cijfers uit het 7400-nummer. Zo is bijvoorbeeld de tweevoudige vier-ingangs TTL-NAND 7420 pin-kompatibel met het CMOS-IC MM74C20N. De maximum-voedingsspanning die deze MM74-IC's kunnen verdragen is 18 V. Deze IC's voldoen ook aan de JEDEC-specs, hoewel dit aan de typenummers niet is te zien.

National IC's zijn, evenals die van sommige andere merken, voorzien van een wat bedrieglijk 'tweede gaatje' dat gemakkelijk verward kan worden met de eigenlijke positioneringsuitholling, die dieper is. Ten overvloede is IC-aansluiting 1 met nog een extra klein putje aangegeven.

Figuur 13. Fairchild Semiconductor heeft een aantal verschillende nummeringen gehanteerd. Herkenbaar zijn de IC's van dit fabrikaat aan de F voor het typenummer. Zowel de F34000-serie als de F4000-serie komen voor, beide gelijk en gebufferd (18 volt). Praktisch alle Fairchild IC's zijn gebufferd, behalve enkele uitzonderingen waarbij het niet mogelijk is (zoals de 4007). Gebufferde IC's zijn tegenwoordig herkenbaar aan een letter B achter het typenummer, ongebufferde IC's aan de aanduiding UB. De toevoeging PC IP = plastic, C = commercial) achter het typenummer duidt op de plastic behuizing en het temperatuurgebied waarbinnen werking gegarandeerd is. Let ook bij Fairchild IC's op het misleidende 'tweede gaatje'.

Figuur 14. Philips en Valvo noemen hun CMOS-IC's LOCMOS (Local Oxidation Complementary MOS), een naam die refereert aan een speciale techniek die de noodzakelijke grootte van de chip sterk reduceert. De eerste drie letters van de typeaanduiding zijn altijd HEF, en het viercijferige typenummer wordt gevolgd door een aantal letters. Direkt na het typenummer van vier cijfers volgt de aanduiding B (gebufferd) of UB (niet gebufferd, bij slechts enkele typen). Ook de aanduiding V komt voor en wordt gebruikt voor gebufferde IC's waarvan de aanbevolen voedingsspanning niet hoger is dan 12,5 V. Voor de andere IC's is deze spanning 15 V. Overigens is de werking van alle LOCMOS-IC's gegarandeerd tot 18 V; de beperking geldt slechts voor de aanbevolen voedingsspanningen. De laatste letter van de typeaanduiding geeft de behuizing aan: P voor plastic, D voor keramisch. Philips houdt zich voor de kodering geheel aan de Pro Electron-norm.

Figuur 15. En nog veel meer ... De genoemde merken vormen slechts een greep uit het hele marktaanbod. Nog veel meer fabrikanten houden zich bezig met de produktie van CMOS-IC's. Signetics, Solitron, Silex en Siltek, om alleen nog maar enkele merken met een S te noemen. Lang niet altijd zijn deze IC's even gemakkelijk te identificeren. In het algemeen echter zal een B in het laatste gedeelte van de typeaanduiding wijzen op een gebufferde uitvoering, terwijl UB meestal wil zeggen dat het om een ongebufferde versie gaat die voor 18 volt geschikt is. De oudere series voor 15 volt worden meestal met A aangeduid.

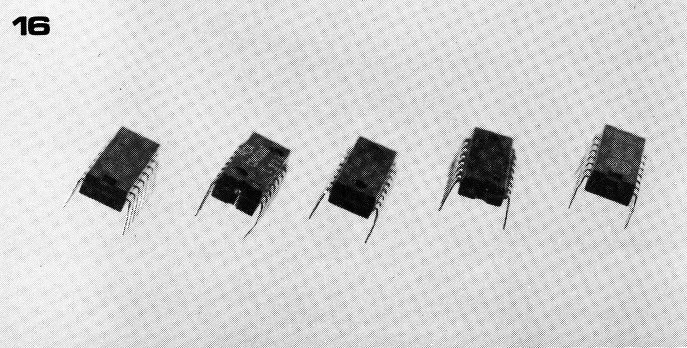

Figuur 16. Let erop dat pen 1 of door de inkeping of door het diepste rondje of door het kleinste hulpgaatje wordt aangegeven. De tekst staat soms ondersteboven.

De omgang met CMOS

CMOS is een haast ideale familie van logische IC's, maar heeft duidelijk een minder plezierige karaktertrek meegekregen: de gevoeligheid voor statische lading. Omdat de ingangsimpedantie zeer hoog (enkele honderden megaohm) en de ingangskapaciteit relatief klein is, kan de potentiaal zeer snel oplopen. Al ongeveer bij 80 volt is dan het leed geschied. Dit voortijdig verscheiden wordt veroorzaakt door het doorslaan van de oxidelaag die de gate isoleert van het substraat.

De fabrikant heeft getracht een bescherming in te bouwen in de vorm van een serieweerstand in kombinatie met een diode naar de plus en min van de voedingsspanning. Te hoge of te lage spanningen worden zo afgeleid naar de voeding. Deze beveiliging werkt uitstekend zolang de stroom door de beveiliging niet groter wordt dan 10 mA. Gewoonlijk heeft de serieweerstand een waarde tussen 100 en 2500 Ω. Dit houdt in, dat bij een spanningsverschil van 100 Ω × 10 mA = 1 V (dus bij een voedingsspanning van 5 volt een ingangsspanning van 6 volt) al het IC kan worden opgeblazen. Is de beschermingsweerstand groter dan 100 Ω, dan ligt dit natuurlijk gunstiger.

Neemt men enkele maatregelen, dan zal het werken met CMOS geen moeilijkheden met zich mee brengen.

- Beveiliging tegen statische elektriciteit:

- Werk niet in ruimten waar statische lading voorkomt (geen kunststof-vloerbedekking). Wat water (met een bloemenspuit) op de vloer doet vaak wonderen.

- Bewaar de IC's in geleidende schuimstof of op een stukje styropor (tempex, piepschuim) waarop een stuk huishoudaluminiumfolie is geplakt met wat sellotape.

- Pak zoveel mogelijk pennen tegelijk vast als het IC in het voetje wordt geplaatst. Houdt met de andere hand de schakeling vast, zodat er via het lichaam een verbinding is tussen IC en schakeling.

- Beveiliging tijdens het werken:

- Schakel de voedingsspanning van de schakeling pas in nadat alle IC's op hun plaats zitten.

- Pas nadat de voedingsspanning aanwezig is, signaalbronnen op de ingang(en) aansluiten om te grote stromen door de beveiligingsweerstanden te voorkomen. Is de signaalbron hoogohmig, dan is dit laatste natuurlijk niet zo belangrijk.

Mocht het voorkomen, dat in de schakeling niet alle ingangen van een CMOS-IC zijn aangesloten, dan zal men spoedig worden verrast door de meest merkwaardige verschijnselen. Zorg ervoor, dat ongebruikte ingangen aan de VDD- of aan de VSS-spanning liggen.

Literatuur

- Application note ICAN 6558 (RCA).

- CMOS databoeken van diverse fabrikanten.