Digitale kristalgenerator

Deze digitale kristalgenerator is een voor laagfrekwente blokvormige signalen uitgewerkte frekwentiesynthesizer. Met vier schakelaars is de uitgangsfrekwentie in te stellen; de stabiliteit en de nauwkeurigheid ervan hangt slechts af van die van de kristaloscillator.

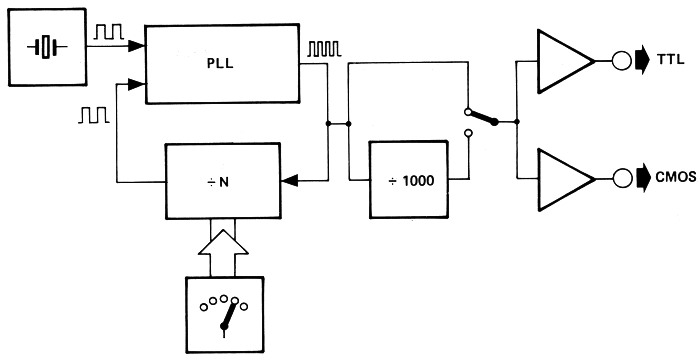

Het blokschema toont dat de schakeling is opgebouwd rond een phase locked loop (PLL). Zo'n PLL is wel wat te vergelijken met een van tegenkoppeling voorziene opamp: zoals deze zijn uitgangsspanning za regelt dat zijn beide ingangsspanningen zoveel mogelijk aan elkaar gelijk zijn, regelt een PLL zijn uitgangsfrekwentie zo dat zijn beide ingangsfrekwenties zoveel mogelijk gelijk zijn. Wanneer we nu, zoals in het blokschema, de uitgangsfrekwentie door een getal N delen en dan aan een van de PLL-ingangen terugvoeren, zal die uitgangsfrekwentievprecies N maal zo hoog worden als de frekwentie op de andere ingang van de PLL. We hoeven er dus alleen voor te zorgen dat die laatstgenoemde frekwentie erg stabiel is, en we hebben een N maal zo hoge frekwentie die net zo stabiel is. Interessanter wordt het nog, wanneer N instelbaar is met een schakelaar: de uitgangsfrekwentie is dan eveneens instelbaar. Voegen we nog een uitschakelbare duizenddeler toe, dan is de uitgangsfrekwentie van de gehele schakeling over een groot bereik zeer stabiel en instelbaar. Het toevoegen van buffers die het signaal op respektievelijk TTL- en CMOS-nivo brengen verhoogt het universele karakter van de schakeling. De uitgangsfrekwentie is in vier cijfers nauwkeurig instelbaar tussen 0,1 Hz en 999,9. kHz.

Figuur 1.

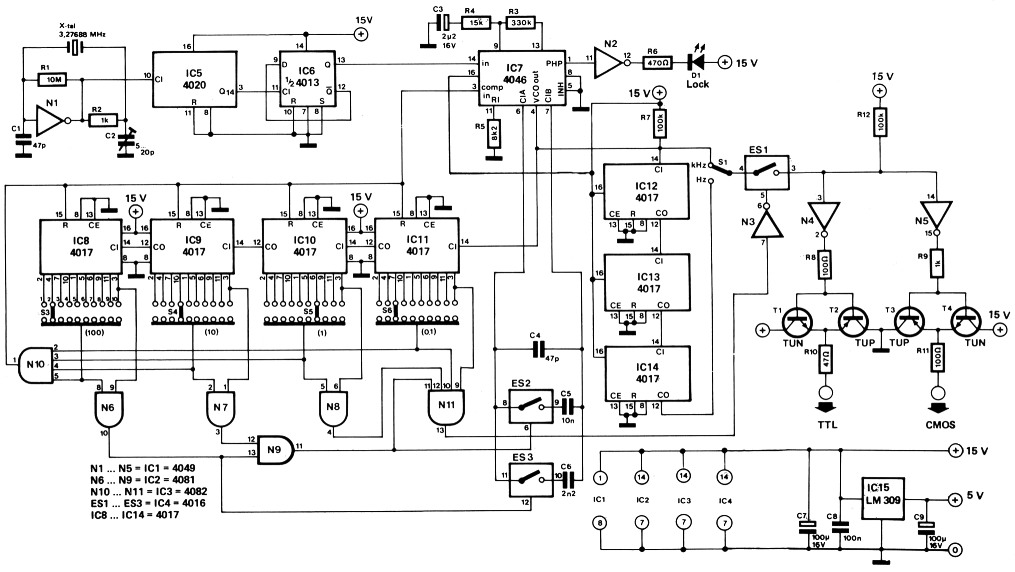

In het gedetailleerde schema zien we dat de "moederoscillator" werkt met een kristal als frekwentiebepalend element en een signaal van 3,2768 MHz levert. Met behulp van IC5 en IC6 wordt deze frekwentie gedeeld door 215 = 32768, zodat we uitkomen op precies 100 Hz. Deze frekwentie komt terecht op de ene ingang van het PLL-IC, IC7. De frekwentiedeler, die de uitgangsfrekwentie door N deelt, is opgebouwd met IC8 ... IC11. Het gewenste deeltal N, en daarmee de uitgangsfrekwentie van de PLL, is instelbaar met de tienstandenschakelaars S3 ... S6. Het uitgangssignaal van de AND-poort N10 dient als tweede ingangssignaal voor de PLL. De PLL zorgt er dus voor dat dit signaal een frekwentie heeft van 100 Hz.

Figuur 2.

De werking van de PLL hangt af van de waarde van een kondensator tussen aansluiting 6 en 7 van IC7. De juiste waarde is op zijn beurt weer afhankelijk van de uitgangsfrekwentie van de PLL, die over een groot gebied kan variëren. Vandaar dat ook de waarde van die kondensatoren eigenlijk moet variëren met de frekwentie. Dat gebeurt met behulp van de elektronische schakelaars ES2 en ES3, die een of twee extra kondensatoren parallel schakelen aan C4. De elektronische schakelaars worden gestuurd door signalen die via poortschakelingen afhangen van de schakelaarstanden.

De eventueel als extra in te schakelen duizenddeler wordt gevormd door de tiendelers IC12 ... IC14. Afhankelijk van de stand van schakelaar S1 levert de schakeling een frekwentie van het met de schakelaars ingestelde getal in Hz of in kHz. De uitgangsbuffers worden gevormd met behulp van buffers en in balans geschakelde transistoren. De uitgangen zijn kortsluitvast. Een extra elektronische schakelaar (ES1) is aangebracht om ervoor te zorgen dat er inderdaad geen uitgangssignaal is wanneer de schakelaars op 000,0 staan. De LED D1 licht op wanneer de PLL "pakt"; in dat geval levert de schakeling de gewenste uitgangsfrekwentie.

De schakeling wordt gevoed met twee voedingsspanningen: een ongestabiliseerde van 15 V en een gestabiliseerde van 5 V. De ongestabiliseerde spanning mag gerust wat hoger gekozen worden; zo kan de schakeling bijvoorbeeld goed gevoed worden uit twee in serie geschakelde negen-volts-batterijen.

R. Dürr & D. Hackspiel