Power-FET's en in het bijzonder D-MOS

De kretologie heeft weer toegeslagen: na V-FET komt HEXFET, D-MOS, T-MOS en SIPMOS, en er zijn nog wel meer namen te bedenken. Al deze vermogens-FET's blijken gelukkig grotendeels gelijk te zijn in hun eigenschappen, zodat het de moeite waard is er eens een artikel aan te wijden waarin wat nader wordt ingegaan op diverse eigenschappen, opbouw en gebruik.

V-FET zal de meeste lezers wel bekend in de oren klinken, hoewel de meesten van u er waarschijnlijk nog nooit een in. het echt hebben gezien. Niet dat dit nu zo'n belevenis is, maar het geeft wel aan dat de V-FET zich toch nooit in een grote belangstelling heeft mogen verheugen. Deze vermogens-FET's die indertijd (zie o.a. ook Elektuur april '76) werden aangekondigd als welhaast ideale eindtransistoren voor (audio)-versterkers, hebben het toch niet helemaal gemaakt, mogelijk voor een groot deel vanwege de prijs en de verkrijgbaarheid. Nu is dit natuurlijk ook een vicieuze cirkel, want komponenten worden pas echt goedkoop en goed verkrijgbaar zodra ze populair zijn. Sinds ongeveer een jaar is de familie van de V-FET uitgebreid met een nieuwe tak, de hierboven genoemde D-MOS-typen. De principiële werking verschilt eigenlijk helemaal niet van die van de V-FET, maar de opbouw is wat anders en de D-MOS-FET's worden nu gebracht (in hoofdzaak tenminste) als snelle schakelaar. Men heeft voorspeld dat een groot deel van de markt voor power-transistoren overgenomen gaat worden door de D-MOS-typen. Er moet dan worden gedacht aan toepassingen in omvormers, schakelende voedingen, relaissturingen en motorbesturing. Daarnaast zijn sommige typen ook geschikt voor hoogfrekwentgebruik, maar die zijn door de fabrikant dan speciaal voor dat doel ontworpen. Voor de hele D-MOSfamilie geldt namelijk weliswaar dezelfde principiële opbouw, maar de verschillende fabrikaten kunnen vooral in de opbouw van de gate verschillen. Zo kan in het algemeen worden opgemerkt dat de V-MOS-FET's geschikter zijn als HF-versterker dan de D-MOS-opvolgers, die daarentegen door hun vlakkere opbouw (zoals nog zal blijken) geschikter zijn voor hogere spanningen. In dit artikel wordt getracht een aantal opmerkingen te maken die algemeen voor de hele familie gelden. En of de fabrikant er nu de naam HEXFET, superFET, SIPMOS, T-MOS of Z-MOS aan heeft gegeven is van minder belang. We gaan hier alleen in op punten waarin de FET's verschillen van de bekend veronderstelde bipolaire transistoren. Degenen die er meer van willen weten kunnen in de literatuurlijst verwijzingen vinden.

Op het moment dat dit artikel is geschreven, zullen er in de detailhandel nog niet veel D-MOS-transistoren verkrijgbaar zijn, en goedkoop zijn ze evenmin. Dat zou echter wel eens kunnen veranderen.

De MOS-FET

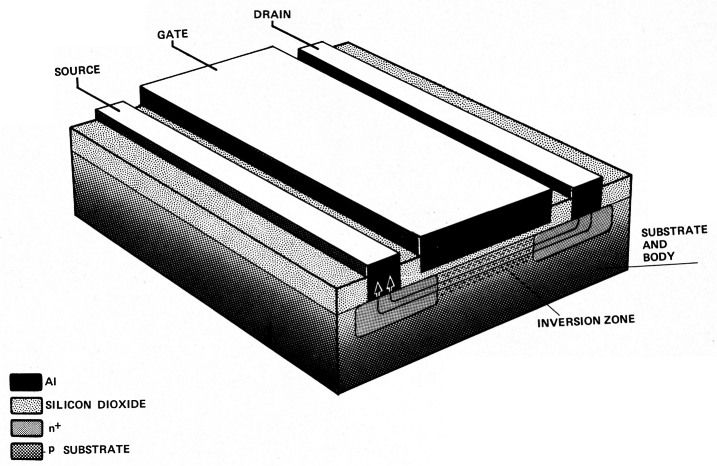

Aangezien de FET nu toch ook weer niet zo'n erg vaak gebruikte komponent is, eerst iets over de eigenschappen van een gewone MOS-FET(1). De MOS-FET heeft een hoge ingangsweerstand, een middelmatige versterking, is geschikt voor hoge frekwenties (tot in de GHz) en kan alleen kleine vermogens aan. Hij wordt dan ook hoofdzakelijk in ontvangers gebruikt. In figuur 1 wordt de werking verduidelijkt.

Figuur 1. De schematische opbouw van een "gewone" FET. Zolang de FET niet geleidt kan hij worden beschouwd als een sperrende diode, bij geleiding verdwijnt deze diode geleidelijk zodat er tenslotte bij volledige geleiding alleen een kleine ohmse weerstand over blijft.

De source en de drain zijn beide aangesloten op een n-gebiedje dat in een p-substraat ligt. Er is dus, net als bij een gewone transistor, sprake van een npn-struktuur. Deze npn-struktuur kan worden voorgesteld als twee tegensteld geschakelde dioden en er kan du n stroom vloeien van drain naar source.

Wanneer de gate positief wordt, verzamelen zich in het p-materiaal langs de gate elektronen (elektronen zijn negatief geladen en worden door de positieve gate aangetrokken). Het p-materiaal langs de gate heeft dan een overschot aan elektronen en is dus eigenlijk geen p-, maar n-materiaal geworden. Tussen source en drain vormt dit een kanaal dat uitsluitend uit n-materiaal bestaat, en dat geleidt! Er kan dan stroom vloeien. Hoe hoger de spanning op de gate, hoe breder het kanaal wordt en hoe lager de weerstand tussen source en drain.

De V-MOS-FET

In figuur 2 is een doorgesneden V-FET getekend. Ook hier scheidt een p-gebiedje de source en de drain, die beide weer met n-gebieden zijn verbonden. Dat de drain met twee soorten n-materiaal (n+ is sterk verontreinigd, n- zwak) is verbonden, is voor het begrip van de werking niet belangrijk. Ook dat de source niet alleen met een n-gebied maar ook met het p-gebied verbonden is hoeft ons niet te verontrusten. Een van de dioden in figuur 1, namelijk degene die in doorlaat staat, is toch overbodig.

Figuur 2. De schematische opbouw van een V-MOSFET. Zolang de FET niet geleidt kan hij worden beschouwd als een sperrende diode, bij geleiding verdwijnt deze diode geleidelijk zodat er tenslotte bij volledige geleiding alleen een kleine ohmse weerstand over blijft.

Vervolgens speelt zich hetzelfde af als in figuur 1: wordt de gate positief, dan ontstaat er een doorlatend kanaal in het p-gebied en er kan stroom lopen tussen drain en source.

Daarmee is de werking van de V-FET verklaard. V staat overigens voor vertikaal en heeft niets van doen met de V-vormige inkeping in het substraat. De stroom loopt vertikaal door het substraat, en daar is de naam V(ertikale)FET van afkomstig.

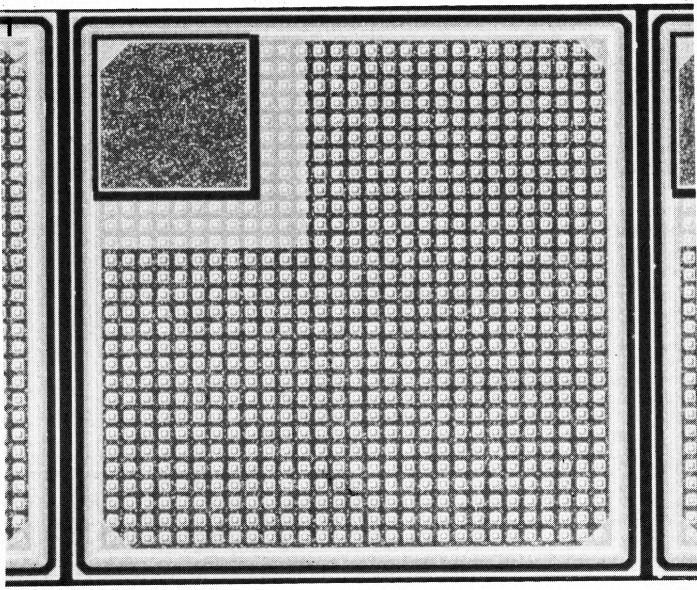

Een interessante kwestie is nu waarom een V-FET wel en een gewone FET nauwelijks vermogens kan verwerken. Die reden is er, technisch gezien, niet zo. De prijs van halfgeleiders wordt echter voor een groot deel bepaald door de afmetingen van de chip, en de chip zou bij een gewone vermogens-FET heel groot worden. Bij de V-FET vervalt het hele oppervlak dat de drain-aansluiting in beslag neemt, want dat ligt nu aan de onderkant. Daar komt nog bij dat de kanalen in de V-FET via diffusie worden gerealiseerd en daarbij kan met veel kleinere toleranties worden gewerkt, waardoor het mogelijk is de FET kleiner te maken. De uiteindelijke power-halfgeleider bestaat uit enkele duizenden FET'jes die allemaal parallel geschakeld zijn, zie foto 1.

Foto 1. Een D-FET bestaat uit een groot aantal FET'jes die allemaal parallel zijn geschakeld. Het vlak linksboven is de gate-aansluiting, terwijl de rest van het bovenvlak de source-aansluiting vormt (de hele bovenkant is immers gemetalliseerd). Foto: Siemens.

Het is dus bepaald niet zo, dat een V-FET in zijn eentje ampères kan verwerken, nee, het is een kwestie van met z'n allen er tegen aan!

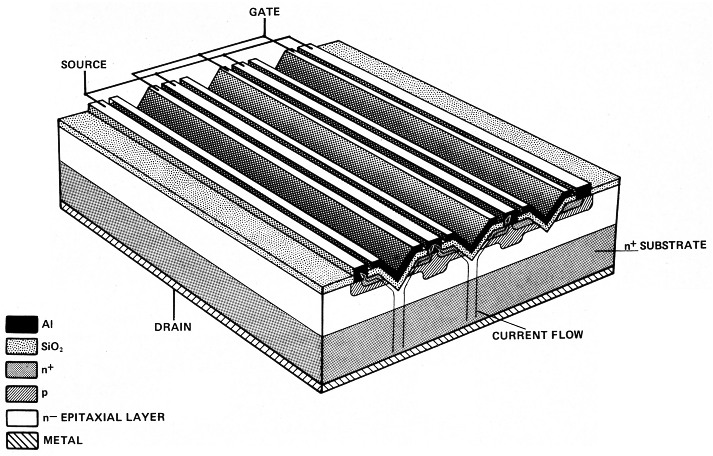

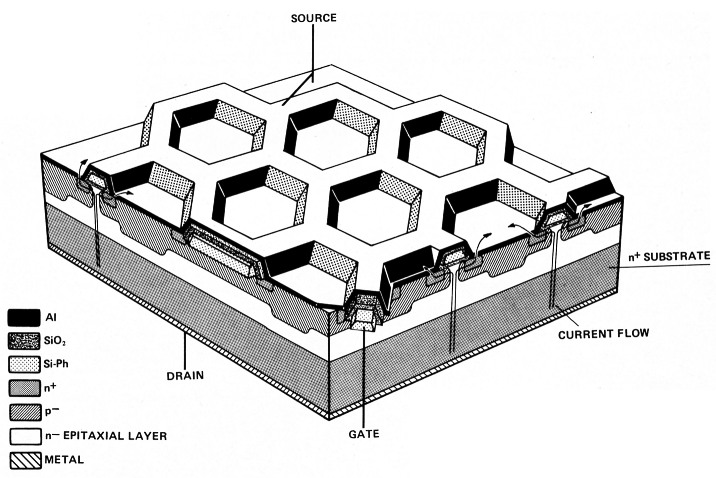

Na deze inleiding levert de echte DMOS-FET ook geen problemen meer op, zie hiervoor figuur 3. De gate is nu in zijn geheel omgeven door een isolerende laag (SiO2) en de source bedekt de hele bovenkant. Was bij de V-FET de gate verdiept aangebracht, bij de D-FET veroorzaakt de gate juist een verhoging, een dijkje. Op foto 1 is de gate als een vierkantje uitgevoerd, maar ook andere vormen zoals zeshoeken (HEXFET) komen voor, iedere fabrikant heeft uiteraard zijn eigen patroon.

Figuur 3. De schematische opbouw van respektievelijk D-MOS-FET. Zolang de FET niet geleidt kan hij worden beschouwd als een sperrende diode, bij geleiding verdwijnt deze diode geleidelijk zodat er tenslotte bij volledige geleiding alleen een kleine ohmse weerstand over blijft.

Tot zo ver de opbouw van de D-FET. Er bestaan nog enkele afwijkende konstrukties die speciaal voor audio of hoogfrekwent zijn ontworpen.

Een nadeel van de beschreven D-MOS-struktuur is dat de gate een zekere inwendige weerstand gekombineerd met een nogal grote kapaciteit (enkele nano-farads) bezit. Hierdoor is het niet denkbeeldig, dat bij aansturing met een MHz-signaal de gate zo heet wordt, dat de hele FET stuk gaat! Hier is de V-FET in het voordeel, want daar kan de gate uit aluminium worden gemaakt en dat levert een aanzienlijk lagere weerstand op. Mogelijk is dit ook de verklaring waarom de D-FETs gepresenteerd worden als schakelaars en niet als HF-komponenten.

De D-FET daarentegen is geschikter voor hogere spanningen. De V-vormige inkeping van de V-FET veroorzaakt grote veldsterkten beneden in de punt en bovendien zijn de diverse opdampen diffusieprocessen beneden in de groef moeilijk in de hand te houden. De vlak opgebouwde D-MOS bezit deze nadelen niet en heeft minder snel last van doorslag.

Eigenschappen

Wat zijn nu de prestaties die van deze nieuwe FET's mogen worden verwacht? Wel, op de eerste plaats: het vermogen dat kan worden gedissipeerd ligt in dezelfde orde van grootte als dat van een transistor die in hetzelfde huis is ingebouwd. Verder zijn er typen die spanningen tot 1000 volt kunnen verdragen en er zijn FET's die wel 25 ampère kunnen regelen. Voor de maximale stroom geldt, net als bij de bipolaire transistoren, dat de stroom kortstondig ook best nog groter mag zijn.

Het is overigens zo, dat de stroom die de fabrikant opgeeft niet zo belangrijk is, het is beter naar de Rds(on) (de weerstand als de FET helemaal open is gestuurd) te kijken. Hoe lager deze is, hoe meer stroom er kan worden verwerkt. Hierbij mag de maximale dissipatie natuurlijk niet worden overschreden!

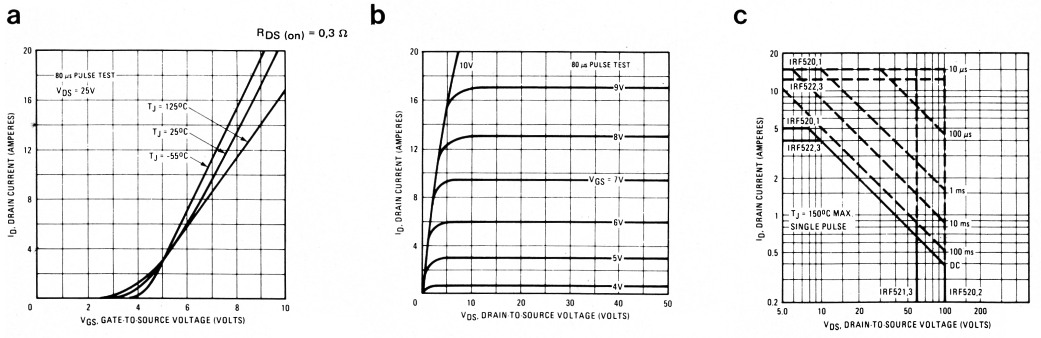

De versterking van FET's wordt uitgedrukt door middel van de steilheid. Die ligt rond een paar ampère per volt, met een drempelspanning van enkele volts. Figuur 4 geeft een voorbeeld.

Figuur 4. De eigenschappen van een FET kunnen uit de karakteristieken worden afgeleid. Voor andere leden van de familie gelden soortgelijke kurves.

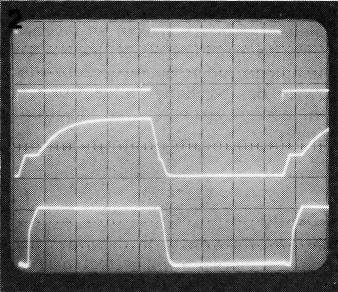

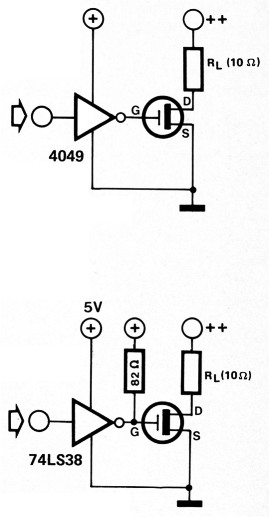

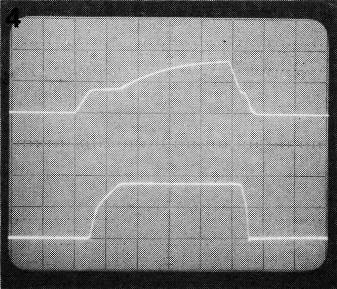

Aangezien het hier een MOS-FET betreft, is er geen vermogen nodig om de gate te sturen, er loopt immers geen stroom. De vermogensversterking van de D-FET's is dan ook ideaal, namelijk oneindig! Helaas blijkt deze eigenschap in de praktijk nauwelijks belangrijk te zijn. Tijdens het schakelen is er wel degelijk vermogen nodig, want de gate heeft een grote kapaciteit van enkele nanofarads die moet worden omgeladen. Gebeurt dit omladen te langzaam, met andere woorden, krijgt de gate een traag veranderende spanning toegevoerd, dan kan de FET natuurlijk ook niet snel schakelen. Uit zichzelf is de hele FETfamilie bijzonder snel (schakelt ampères in enkele tientallen nanosekonden), maar die snelheid wordt alleen gehaald bij een ideaal rechthoekig stuursignaal op de gate. En in de praktijk ziet zo'n gate-spanning er allesbehalve fraai uit. Foto 2 geeft hiervan een (wat overdreven) voorbeeld. Het bovenste spoor geeft een mooie rechthoekspanning die een CMOS 4049-inverter aanstuurt. De uitgang van de 4049 is rechtstreeks verbonden met de gate van een D-MOS-FET (in dit geval BUZ10). De flanken zijn niet erg mooi en ongeveer halverwege komen er vreemde horizontale stukjes in de kurve voor. Het onderste signaal is de stroom door de FET.

Foto 2. Bij aansturing van een vermogensFET door CMOS ontstaan aanzienlijke vertragingen omdat de driver te weinig stroom kan leveren om de gate-kapaciteit snel om te kunnen laden. Van boven naar beneden: sturing CMOS-buffer, signaal op de gate van de FET en de stroom door de FET.

Het is duidelijk dat de CMOS-inverter nogal wat tijd nodig heeft om de gate-spanning te veranderen, want de gatekapaciteit kan met maar enkele milliampères worden omgeladen. Omdat de 4049 bedoeld is als buffer voor aanpassing op TTL-schakelingen kan hij meer stroom naar massa laten lopen dan naar de plus. Vandaar dat de negatieve flank veel steiler is dan de positieve.

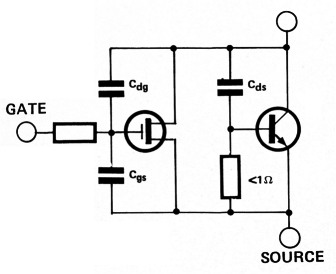

Dan rest nog de verklaring waar dat merkwaardige vlakke stukje door wordt veroorzaakt dat in beide flanken voorkomt, maar het best zichtbaar is in de langzamere positieve flank. Hiervoor is grotendeels de gate-drain-kapaciteit verantwoordelijk. In figuur 5 is een vereenvoudigd vervangingsschema getekend en de buizenliefhebbers (zijn die er nog?) zullen onmiddellijk aan het zogenaamde miller-effekt denken.

Figuur 5. Een sterk vereenvoudigd vervangingsschema van een D-FET. Voor de aansturing is vooral de kapaciteit naar drain en source van belang. Parallel aan de FET staat een transistor die bij negatieve drain-spanningen als een diode werkt (via de weerstand van 1 Ω en de basis-kollektorovergang) Deze diode kan dezelfde stroom verwerken als de D-FET, maar is wel aanzienlijk lager.

De stijgende spanning op de gate heeft tot gevolg dat de drain-spanning zakt. Deze variatie wordt via de gate-drainkapaciteit doorgegeven naar de gate en hierdoor kan de gatespanning maar heel langzaam toenemen. Dit blijft zo, totdat de drainspanning niet kleiner meer kan worden. Op foto 2 is dit effekt duidelijk herkenbaar: alleen tijdens het veranderen van de drainspanning is de gatespanning nagenoeg konstant. Daarnaast is er ook altijd wel enige induktiviteit in de source-leiding die dit effekt versterkt door de source een beetje negatief te maken.

Bij een hogere voedingsspanning zal het uiteraard langer duren om de gatedrain-kapaciteit om te laden.

De uiteindelijke schakeltijd wordt dus in hoofdzaak bepaald door het circuit dat de gate aanstuurt. De bereikte tijd hangt af van de drain-source-spanning (hoe hoger, hoe langer het duurt), de gate-kapaciteiten (zijn afhankelijk van de gebruikte FET) en het aanstuurcircuit (dat hebt u zelf in de hand).

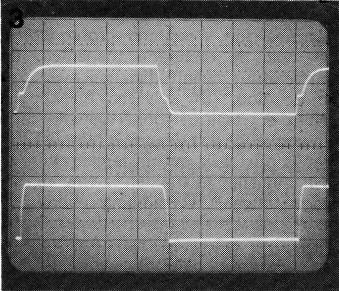

Foto 3 toont aansturing door TTL, en dat gaat al een stuk sneller. Dit snelle schakelen brengt een paar problemen met zich mee. Wanneer er een paar ampère door de FET loopt en die stroom wordt in nanosekonden onderbroken, dan is er maar akelig weinig zelfinduktie in het drain-circuit nodig om een flinke piekspanning op te wekken. Deze piekspanning moet bij de voedingsspanning worden opgeteld, en is deze som hoger dan de toelaatbare drain-source-spanning van de FET, dan sneuvelt deze onmiddellijk. Oplossingen hiervoor zijn een zorgvuldige opbouw (ook bij experimenten), samen met een vrijloopdiode naar de voeding, of een zenerdiode parallel aan de FET, of zelfs een RC-netwerkje parallel. Deze laatste oplossing is eigenlijk niet aan te raden, want er ontstaat toch altijd een uit-dempende oscillatie die bij een ongelukkig gekozen RC-tijd zelfs erger zou kunnen zijn dan de kwaal.

Foto 3. Aansturing via een TTL openkollektor-buffer levert al betere tijden op. De spanning voor de gate-sturing kan het beste gelijk worden gekozen aan twee maal de spanning waarbij de FET wordt opengestuurd. Dit levert nagenoeg gelijke flanken in de drainstroom op. Een hogere spanning laat het vermogen dat nodig is om de gate aan te sturen snel (met het kwadraat van de spanning) toenemen en levert geen tijdwinst op.

Daarnaast wordt door deze piek in de drainspanning ook de gate-spanning via de drain-gate-kapaciteit beinvloed. Wordt de gate hoogohmig aangestuurd, dan kan gemakkelijk de maximale gatesource-spanning worden overschreden, hetgeen tot gevolg heeft dat u een nieuwe FET moet kopen. Oplossingen zijn: de gate laagohmig aansturen en/of een zener tussen gate en source.

Uit bovenstaande kan eigenlijk al worden opgemaakt dat deze vermogensFET's geen interne beschermdioden (zenerdioden) bezitten. Dit is juist mogelijk door de relatief grote kapaciteit van de gate. Hierdoor is er een flinke statische lading nodig om de spanning te hoog te laten worden. Het ontbreken van de dioden heeft als voordeel, dat de ontwerper nu veel vrijer is bij het aansturen van de gate; met name niet al te grote negatieve spanning veroorzaken nu geen problemen meer. Bij de omgang met D-MOS is dus wel de normale voorzichtigheid met betrekking tot statische ladingen vereist!

Figuur 6a en 6b. Wanneer men niet al te hoge eisen stelt aan de schakelsnelheid kan D-MOS zeer eenvoudig worden gestuurd. In figuur 6a direkt vanuit een CMOS-poort met een voedingsspanning van zo'n 10 volt. In figuur 6b vanuit TTL met een open-kollektoruitgang. Het zal in de meeste gevallen nodig zijn de pull-up-weerstand te voeden uit een hogere spanning dan de 5 volt TTL-voeding.

Foto 4. De gate-spanning tijdens het schakelen. De exakte tijdvertraging is moeilijk te voorspellen omdat de betrokken gatekapaciteiten afhankelijk zijn van de (momentele drain-spanningen. Voor het benodigde stuurvermogen geldt dit ook, vandaar dat sommige fabrikanten grafieken verstrekken van de vorm van de gate-spanning bij verschillende drain-spanningen.

Parallel schakelen

Parallel schakelen van D-FET's levert normaal gesproken geen problemen op, omdat het halfgeleidermateriaal bij toenemende temperatuur een hogere weerstand vormt; de Rds(on) neemt dan toe. Hierdoor zal de warmste transistor automatisch minder stroom verwerken, waardoor zijn dissipatie afneemt. Ook figuur 4a is in dit verband belangrijk: de maximale stroom is bij een hoge temperatuur lager. Bij stromen onder 2 ampère is dit overigens omgekeerd.

Tot zo ver is er geen vuiltje aan de lucht. Wanneer de FET's die parallel worden geschakeld echter nogal verschillende Vgs-karakteristieken bezitten, dan wordt de FET met de laagst vereiste gate-spanning het eerst ingeschakeld en moet deze tijdelijk het werk alleen doen. Een tweede probleem kan oscillatie op zeer hoge frekwenties (meer dan 100 MHz) zijn. Het is dus toch wel aan te raden de FET's enigszins (≈5%) op gelijke Vgs uit te zoeken en daarnaast kleine weerstandjes op te nemen in de leiding naar iedere gate. Hierdoor wordt zowel de oscillatie onderdrukt als een betere verdeling van de sturing bereikt.

Koeling

De D-FET's worden in dezelfde behuizing als bipolaire transistors geleverd. Ze kunnen op eenvoudige wijze, al dan niet geisoleerd, op een koelplaat worden geschroefd.

Maar de koeling is bij FET's veel belangrijker dan bij de gewone transistors. Er is bij het parallel schakelen al opgemerkt dat de Rds(on) een positieve temperatuurkoëfficient bezit en dat was gunstig (voor het parallelschakelen tenminste). Voor de dissipatie is dit gedrag juist erg vervelend. Naarmate de FET heter en daarmee zijn weerstand groter wordt, zal ook de dissipatie toenemen. De temperatuur neemt dan nog meer toe, en zo door. Er kan een meekoppeleffekt ontstaan dat onherroepelijk leidt tot vernieling van de mooie dure D-FET. Het is dus zaak om de temperatuur zo laag mogelijk te houden, zowel om de laagst mogelijk verzadigingsspanning te verkrijgen als wel om oververhitting te vermijden. Een goede vuistregel voor de praktijk is: de koelplaat gewoon de helft groter nemen.

Literatuur

Uitstekende lektuur is het "HEXFET databook" van International Rectifier. Ook de "VMOS Power FET's Design Catalog" van Siliconix geeft veel informatie (over V-FET's).

Verder:

- "VMOS-Transistoren, Eigenschaften and Schaltungsbeispiele" van ITT.

- "Hitachi Power MOSFET's" van Hitachi.

- "SIPMOS Leistungstransistoren" van Siemens