EPROM-programmer voor Z80

Programmeer-schakeling voor 2716-EPROM's

Door gebruik te maken van de WAIT-ingang van de Z80-microprocessor is deze kleine schakeling in staat om de bijzondere volgorde van de stuursignalen van de Z80 aan te passen tot bruikbare programmeersignalen voor een 2716. Het gebruikte Z80-systeem moet daarvoor wel zijn voorzien van een statisch RAM-geheugen.

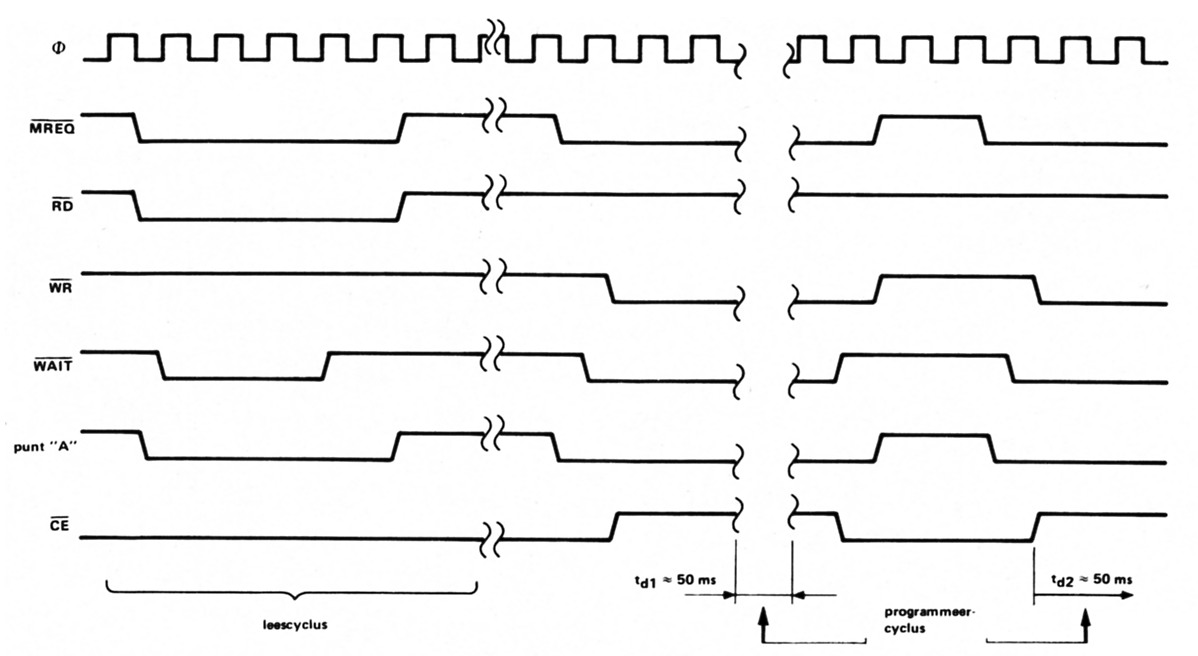

Om een 2716-EPROM te kunnen programmeren moeten de volgende signalen op de aansluitpennen van deze EPROM worden gezet: Op pen OE (output enable) moet een "1"-nivo komen te staan, data en adres moeten gedurende de programmeercyclus stabiel blijven, pen Vpp. moet een programmeerspanning van 25 V krijgen en tenslotte moet pen CE (chip enable) logisch een zijn gedurende minstens 50 ms. Niet moeilijk, maar al die voorwaarden moeten wel strikt worden aangehouden. Verder moet de snelheid van de processor worden aangepast en moeten we letten op enkele bijzonderheden in de volgorde van de kontrolesignalen. Zo is bijvoorbeeld in figuur 1 te zien dat bij een lees-cyclus het RD-signaal (read) op hetzelfde moment verschijnt als het MREQ-signaal (memory request). Bij een schrijfcyclus is er een vertraging van een klokperiode tussen het verschijnen van MREQ en het logisch nul worden van het WR-signaal (write). Daar moet rekening mee worden gehouden, want het programmeren bestaat in feite uit een verlengde schrijf-cyclus. Verder moet de EPROM ergens in het adresseerbare geheugenbereik worden gezet. Daarbij is een adresdekoder nodig (hier niet getekend) die het enable-signaal voor de EPROM levert.

Figuur 1. Tijdvolgorde-diagram van de benodigde Z80-signalen voor het lezen en schrijven in het geheugen. Let op dat WR iets later dan MREQ verschijnt, terwijl RD tegelijk met MREQ schakelt. Door een vertragingsschakeling wordt het WAIT-signaal "0" gehouden als de EPROM wordt geadresseerd, zowel bij een lees- als een schrijfcyclus.

De schakeling en zijn werking

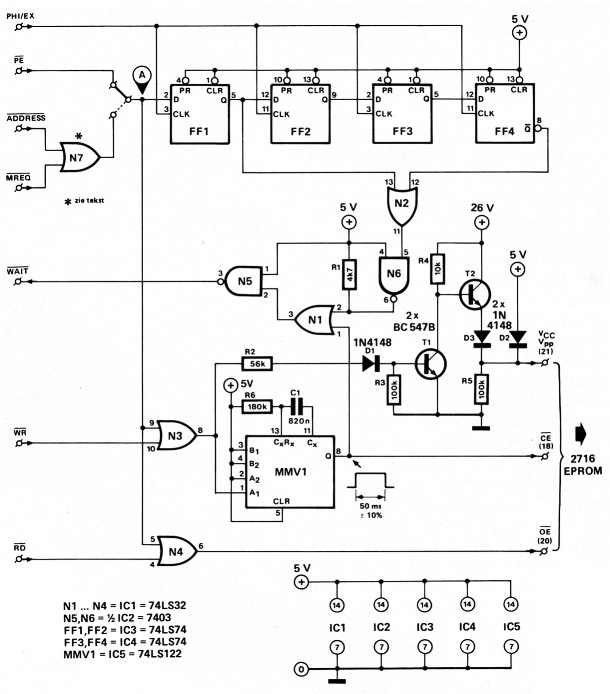

Het adresdekodeersignaal moet komen te staan op punt A in het schema van figuur 2 (logisch nul-nivo). Als het signaal wordt gemaakt uit een kombinatie van de adreslijnen en de MREQ-lijn, dan kunnen deze samengevoegd worden door middel van poort N7. Ook een eventueel reeds aanwezig ADDRESS-signaal kan aan deze poort worden toegevoegd. Tenslotte kan in sommige gevallen ook het PE-signaal (program enable) worden gebruikt als enable-signaal voor de EPROM.

Figuur 2. Het schema van de 2716-EPROMprogrammer voor Z80. De schakeling bestaat uit een monostabiele multivibrator die een "gekalibreerde" programmeer-impuls van 50 ms levert en een vertragingsschakeling voor het WAIT-signaal.

De schrijfcyclus

Als de EPROM wordt geadresseerd ontstaat aan de uitgang van poort N3 een neergaande flank, waardoor de monostabiele multivibrator MMV1 wordt getriggerd. Aan de uitgang van de MMV (pen 8) verschijnt dan een impuls met een lengte van 50 ms, die dient als programmeer-impuls voor de CE-ingang van de EPROM. Datzelfde signaal houdt de WAIT-ingang van de Z80 50 ms lang "laag" (via N1 en N5), zodat adressen en data op de bus in die tijd stabiel blijven. Daar RD tijdens het schrijven "1" is zal de OE-ingang van de EPROM ook logisch een zijn. Gedurende deze tijd spert T1, zodat T2 kan geleiden en de spanning op aansluiting Vpp van de EPROM stijgt van 5 naar 25 V.

Die situatie zal zo blijven zolang het WR-signaal aanwezig is. De uitgang van N3 kan namelijk niet logisch nul worden zolang de WR-lijn niet logisch nul wordt. Bovendien zitten we ook nog met de vertraging van MMV1. Daarom is een vertragingsschakeling toegevoegd. Deze bestaat uit de flipflops FF1 ... FF4, die de WAIT-ingang van de Z80 enkele klokperioden lang logisch nul houden nadat punt A "0" is geworden. De maximale vertraging tussen het moment waarop de WAIT-ingang nul wordt (het "bevriezen" van adressen en data) en het moment waarop de WR-lijn nul wordt bedraagt circa 150 ns. Daar kunnen we nog enkele tientallen nanosekonden vertraging van MMV1 aan toevoegen. Met de vier flipflops komen daar nog drie wacht-cycli bij, dus 750 ns bij een klok van 4 MHz.

Zoals het tijdvolgordediagram in figuur 1 laat zien wordt de WAIT-ingang pas nul na het aktief worden van MREQ, terwijl de WR-lijn gewoon logisch een blijft. Bij de komst van de CE-impuls van 50 ms zijn de adres- en databus "bevroren" en blijven adressen en data tijdens de hele programmeertijd aanwezig.

De leescyclus

De vertragingsschakeling wordt geaktiveerd door het adresdekodeersignaal; ze werkt dus ook tijdens een leescyclus van de EPROM. Dat betekent dat we zonder problemen een EPROM met een lange toegangstijd (450 ns) kunnen lezen. De MMV wordt bij het lezen niet getriggerd, zodat CE logisch nul blijft. Dat is ook te zien in het tijdvolgordediagram (vooraan). Verder wordt OE nul omdat RD logisch nul wordt. De EPROM zet de bij het aangeboden adres behorende data dan op de bus.

Als men de normale leessnelheid wil aanhouden, dan kunnen de wachtcycli vervallen. Daarvoor hoeft men alleen maar een verbinding te leggen tussen pen 6 van N4 (OE) en pen 4 (PR) van FF1. Die laatste pen is dan niet meer verbonden met +5 V.

Het programmeren

Uit het voorgaande is wel gebleken dat het hier niet om een zelfstandige schakeling gaat, maar om een hulpschakeling die bijvoorbeeld tussen de EPROM en het voetje waarin de EPROM normaal wordt gestoken kan worden opgenomen. Er hoeven dan maar enkele extra-verbindingen te worden gemaakt: PHIEX (klok), WAIT, RD, WR, het adresdekodeersignaal (of PE) en tenslotte de programmeerspanning van 26 V (iets hoger dan de benodigde 25 V in verband met de spanningsval over D2 en T2). Pas op dat het adresdekodeersignaal niet het RD-signaal bevat, anders is een schrijfoperatie niet mogelijk en kan er dus ook niet geprogrammeerd worden.

Een mooi voorbeeld voor het gebruik van deze programmer vormt de preset-unit voor de polyfone synthesizer, die deze maand en volgende maand in Elektuur wordt beschreven. Hierbij is het niet eens nodig om een extra voetje voor de te programmeren EPROM te gebruiken: de EPROM kan in het voetje voor de RAM (IC9) op de geheugenprint worden gestoken (het hierbij behorende schema komt volgende maand in het tweede deel van de preset-unit). IC6 wordt zo lang verwijderd (4071) waarna het voetje voor IC6 gebruikt kan worden voor de volgende aansluitingen naar de EPROM: pen 10 (IC6): OE (pen 20 van EPROM) pen 11 (IC6): Vpp (pen 21 van EPROM) pen 4 (IC6): CE (pen 18 van EPROM) Het kloksignaal PHIEX is beschikbaar op pen 27a van de µP-bus. Signaal RD zit op pen 31c en WR op pen 31a. Het PE-signaal staat aan de uitgang van N10. Het WAIT-signaal wordt op pen 5c van de 64-polige konnektor aangesloten. Als nu de program-meerspanning aanwezig is wordt elke schrijfopdracht (store enable) in het geheugen "vertaald" in een programmeeroperatie in de EPROM.

B. Barink.