Logische familie aangelegenheden

Een digitaalhuwelijksburo.

Het koppelen van digitale IC's binnen een logische familie zal in de praktijk niet snel tot problemen leiden, zolang maar rekening wordt gehouden met fan-out en (parasitaire) bedradings- en ingangskapaciteiten. Lastiger wordt het als verschillende logische families door elkaar gebruikt worden, zoals TTL (standaard, LS en ALS) en CMOS. En het aantal kombinatiemogelijkheden breidt zich uit met het groter worden van de logische stamboom. Zo konden we onlangs de geboorte aankondigen van high speed CMOS (HC-MOS), die ook weer in twee varianten op de markt is. Hoe staat het met de kompatibiliteit van al deze families? Of: hoe digitaal is digitaal? Voor wie er het fijne van wil weten is een duik in de databoeken onvermijdelijk.

Digitale elektronica mag zich verheugen in een grote populariteit. De reden daarvan is niet zo moeilijk te raden: omdat de signalen of logisch 1, bf logisch 0 zijn (en niets daar tussen in), is het ontwerpen en het fout-zoeken relatief eenvoudig.

Zolang het "in de familie" wordt gehouden, dus bijvoorbeeld alleen met TTL of met CMOS wordt gewerkt, heeft de fabrikant ervoor gezorgd dat er geen problemen zullen ontstaan. De logische nivo's zijn duidelijk gedefinieerd en de in- en uitgangsstromen zijn op elkaar aangepast.

Maar nu de kombinatie van verschillende logische families. Daar komt worst case design bij om de hoek kijken, een kreet inherent aan analoog ontwerpen en daarom door digi-freaks geschuwd als de pest. Toch maar even doorbijten.

Even voorstellen?!

Het feit dat er zoveel verschillende logische families zijn heeft natuurlijk zijn oorzaken. Die kunnen worden samengevat met snelheid en zuinigheid. In de race naar steeds kortere schakeltijden bij een steeds kleinere vermogensdissipatie is de ene na de andere serie logische IC's ten tonele verschenen. Om praktische redenen en vanwege de gewenste overzichtelijkheid kunnen niet alle families en alle mogelijke kombinaties behandeld worden. Daarom is een selektie gemaakt van de op dit moment (of in de nabije toekomst te verwachten) meest voorkomende series voor de amateur. Een overzicht hiervan met hun kenmerkende gegevens staat in tabel 1. Die gegevens moeten als richtlijn beschouwd worden; ze dienen voor een globale vergelijking. Afhankelijk van bedrijfskondities en fabrikaat kunnen kleine verschillen optreden.

| TTL | CMOS | |||||

|---|---|---|---|---|---|---|

| Serie | 7400 | 74LS | 74ALS | 4000 | 74HC | 74HCT |

| Voedingsspanning | 5 V | 5 V | 5 V | 3-18 V | 2-6 V | 5 V |

| Dissipatie per poort | 10 mW | 2 mW | 1 mW | 2,5 nW | 2,5 nW | 2,5 nW |

| Poortvertragingstijd | 10 ns | 9,5 ns | 4 ns | 40 ns | 9 ns | 9 ns |

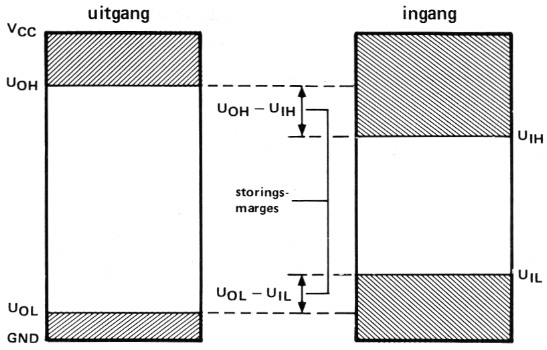

De logische 1 en de logische 0 waarop het digitaal denken gebaseerd is, moeten voor de konkrete realisatie in spanningsnivo's vertaald worden. De daarbij te definiëren spanningen staan in figuur 1.

Figuur 1. De logische nivo's vertaald in konkrete spanningen. Tussen "hoog" en "laag" is een verboden gebied.

Voor een goed funktioneren van de schakeling in alle omstandigheden (worst case) moet UOH altijd groter zijn dan UIH en UOL altijd kleiner dan UIL. Tabel 2 is een overzicht van de hier behandelde families met hun bijbehorende nivo's. De nivo's van CMOS zijn alleen bij 5 V gegeven omdat we TTL-kompatibiliteit willen bezien.

| TTL | LS-TTL | ALS-TTL | CMOS | HCT-MOS | HC-MOS | ||

|---|---|---|---|---|---|---|---|

| 5 V ±5% | 5 V ±5% | 5 V ±5% | 3...18 V | 5 V ±10% | 2...6 V | ||

| VCC | 5 V | 5 V ±10% | 3 V | ||||

| UIH - ingangsnivo logische 1 (min) | 2,0 V | 2,0 V | 2,0 V | 3,5 V | 2,0 V | 3,15 V | 2,1 V |

| UIL - ingangsnivo logische 0 (max) | 0,8 V | 0,8 V | 0,8 V | 1,5 V | 0,8 V | 1,1 V | 0,6 V |

| UOH - uitgangsnivo logische 1 (min) | 2,4 V | 2,7 V | 2,7 V | 4,5 V | 3,7 V | 3,7 V | 2,2 V |

| UOL - uitgangsnivo logische 0 (max) | 0,5 V | 0,5 V | 0,4 V | 0,4 V | 0,4 V | 0,4 V | 0,4 V |

| IIL (Isink-ingang) (max) | -1,6 mA | -0,36 mA | -0,2 mA | -0,005 µA | |||

| IIH (Isource-ingang) (max) | 40 µA | 20 µA | 20 µA | 0,005 µA | |||

| IOL (Isink-uitgang) (min) | 16 mA | 8 mA | 4 mA | 0,4 mA | 4 mA | 4 mA | 4 mA |

| IOH (Isource-uitgang) (min) | -400 µA | -400 µA | -400 µA | -0,4 mA | -4 mA | -4 mA | -4 mA |

Kombinatiemogelijkheden

Allereerst gaan we bekijken welke families louter afgaande op de in- en uitgangsnivo's elkaar zonder problemen "verstaan". Uiteraard (en gelukkig) geeft uitwisseling binnen de TTL-groep geen problemen. In een enkel geval zal er iets aan storingsmarge gewonnen worden, namelijk daar waar standaard TTL plaats maakt voor LS- of ALS-TTL. Ook de HCT-MOS (de high speed CMOS die TTLkompatibel is) laat zich zonder meer met TTL koppelen. Sterker nog, de gebruiker hoeft er helemaal geen weet van te hebben dat ie met CMOS aan het werken is, zijn poortjes gedragen zich gewoon als extra zuinige LS-TTL-circuits. De tolerantie op de voedingsspanning mag bij HCT-MOS bovendien groter zijn dan bij TTL (10% tegen 5%), hetgeen betekent dat een voeding die voldoet aan TTL-eisen zeker zal voldoen aan HCT-eisen.

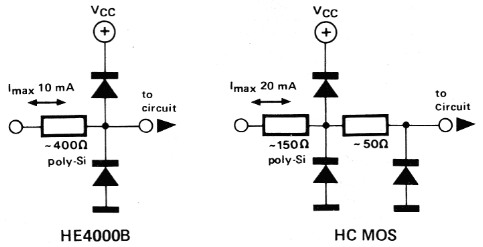

I Van TTL naar CMOS, dat is een kombinatie die niet gaat zonder voorzorgsmaatregelen. De UOH van TTL is in alle gevallen lager dan de UIH van CMOS bij een voedingsspanning van 5 V. Daarom zal een "logische 1" op een TTL-uitgang niet altijd door de CMOSingang als "hoog" geïnterpreteerd worden. Hetzelfde geldt als we HC-MOS met TTL willen aansturen die op 5 V werkt. In dit geval is UIH minimaal 3,15 V, hetgeen TTL toch weer boven de pet gaat. Hier is echter wel een mouw aan te passen. HC-MOS is geschikt voor voedingsspanningen van 2 .... 6 V. Staat het HC-MOS-gedeelte op 3 V te draaien, dan komt UIH op 2,1 V te liggen (70% van 3 V). Nu is TTL wel in staat een logische 1 te leveren, en wel met een storingsmarge van 0,3 V. Wel treedt hier de situatie op waarin het TTL-uitgangsnivo hoger kan komen te liggen dan de HC-MOSvoedingsspanning. In dat geval gaat er een stroom lopen door de 150 St ingangsweerstand en de ingangsprotektiediode (figuur 2), De grootte van die stroom wordt begrensd door de kollektorweerstand in het uitgangscircuit van de TTL poort en die 150 Ω. Zolang de ingangsstroom de 20 mA niet overschrijdt, en dat zal normaal gesproken niet gebeuren, is er niets aan de hand. Wat betreft de logische nul in deze situatie (we hebben het nog steeds over TTL HC-MOS) wordt het dringen: UIL is namelijk maximaal 0,6 V (20% van 3 V), terwijl de UOL van TTL 0,5 V is, hetgeen ons een storingsmarge van 0,1 V overlaat.

Van CMOS en HC-MOS naar TTL geeft gelukkig minder problemen, aangenomen tenminste dat die CMOS op een 5 V voeding werkt. TTL stelt niet zulke hoge eisen aan de ingangsnivo's; UIL ligt relatief hoog en UIH relatief laag. De CMOS-uitgangsspanningen sluiten daarom zonder meer aan op wat voor TTL vereist is, maar we moeten op onze hoede zijn of de CMOS de relatief grote TTL-ingangsstromen wel kan leveren (of opnemen). Dat geldt met name als gewone CMOS geacht wordt standaard-TTL aan te sturen. Onder de kop "fan-out" gaan we daar dieper op in.

Onnodig te vermelden dat wanneer het CMOS-gedeelte op een hogere voedingsspanning (bijv. 15 V) werkt, er bij de koppeling met TTL of HCT-MOS een nivo-aanpassing gerealiseerd moet worden, en wel met een zogenaamde level shifter.

Figuur 2. Ingangsprotektie bij CMOS en HC-MOS circuits.

Fan-out

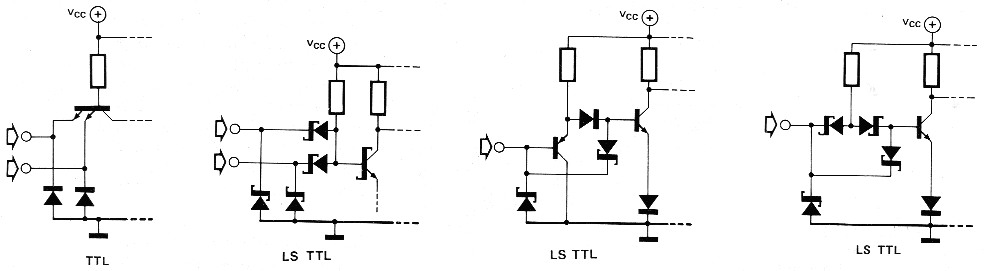

Wat betreft de ingangsstroom moet er een onderscheid gemaakt worden tussen TTL en CMOS. TTL-ingangen zijn uitgevoerd met een (multi-emitter)transistor waarvan de basis via een weerstand naar VCC is geschakeld (figuur 3). Dat heeft tot gevolg dat een vrijhangende ingang overeenkomt met logisch 1. Een logische 0 maakt men door de ingang naar massa te trekken. Daarbij loopt er een stroom uit de ingang, de zogenaamde sink-stroom. Bij standaardTTL is die sink-stroom 1,6 mA, bij LS-TTL 0,4 mA en bij ALS-TTL 0,2 mA. Deze waarden zijn ook vermeld in tabel 2. De uitgang van de aansturende poort moet deze sink-stroom kunnen verwerken. Voor TTL is dat natuurlijk geen probleem (de uitgangen zijn erop berekend) maar CMOS wil nog wel eens in de problemen komen. Niet zo vreemd, want als we het bij CMOS in de familie houden wordt er van de uitgang helemaal niet verlangd dat er "grote" stromen geleverd worden. Alleen de laadstromen van de ingangskapaciteiten (en de bedrading) zullen lopen en voor het overige slechts de ingangslekstroom, en die is in de orde van grootte van enkele nA's.

Figuur 3. Verschillende konfiguraties van (LS-) TTL-ingangen. Als de ingang "laag" gemaakt wordt loopt er een relatief grote stroom uit de ingang (sink-current).

Voor het berekenen van de fan-out in het algemeen, dus ook in inter-familiale gevallen, kan de maximaal leverbare uitgangsstroom gedeeld worden door de benodigde ingangsstroom. Deze stromen zijn gedefinieerd voor zowel het hoog als het laag nivo (zie tabel 2). Volgend uit de opzet van het TTL-ingangscircuit hebben we al gezien dat de IIL van een TTL-poort aanmerkelijk groter is dan de IIH. Vanwege dit niet symmetrisch zijn van de ingangsstroom moet de fan-out bij beide logische nivo's berekend worden. De kleinste hieruit volgende waarde moet aangehouden worden.

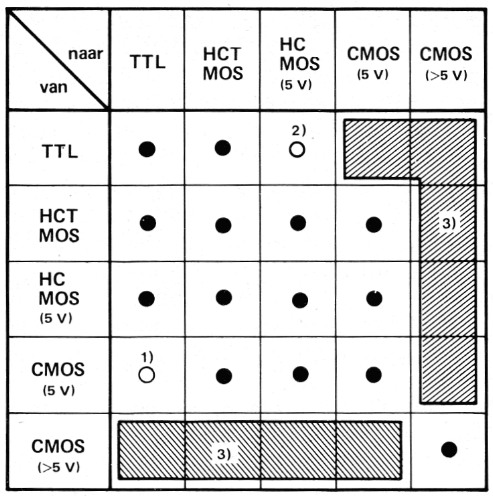

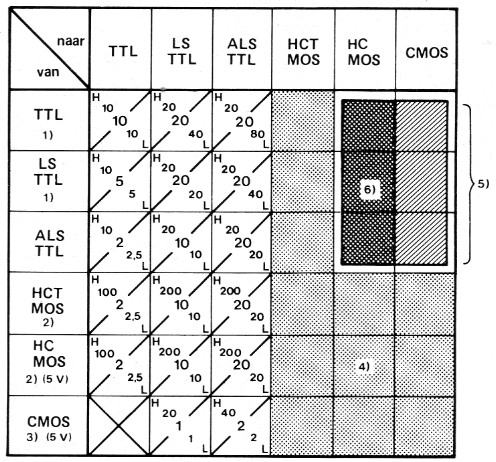

Aan de hand van de gegevens uit tabel 2 is het mogelijk de fan-out bij de verschillende kombinaties te berekenen. Voor het overzicht zijn die resultaten in een aparte tabel vermeld: tabel 4. De fan-out is alleen berekend voor die kombinaties die wat betreft de logische nivo's rechtstreeks op elkaar passen (zie tabel 3).

1) Wat nivo's betreft mogelijk, maar beperkte mogelijkheden i.v.m. sink-current; bufferen!

2) Wel mogelijk indien het HC-MOS-gedeelte wordt gevoed met 3 V.

3) Niet mogelijk zonder extra aanpassingen.

We zien in tabel 4 dat TTL, vanwege de grote sink-stroom, "zwaar aanstuurbaar" is. De fan-out is, als er gewone TTL aangestuurd wordt, in de regel laag. CMOS is zelfs niet in staat om de sink-stroom van 1,6 mA op te nemen. Vandaar dat de rechtstreekse koppeling CMOS-TTL, die wat betreft de spanningsnivo's nog wel mogelijk was, geen doorgang kan vinden. Er zijn echter fabrikanten die CMOS-IC's leveren met gebufferde outputs die weer wel 1,6 mA sink-stroom kunnen opnemen. En anders is het ook nog mogelijk om CMOS-uitgangen parallel te schakelen tot de gewenste IIL gehaald wordt. Hierbij zullen echter onvermijdelijk de databladen van de betreffende fabrikant geraadpleegd moeten worden. Het uitsturen van LS-TTL en ALS-TTL verloopt minder problematisch vanwege de kleinere sink-stroom. Ook CMOS is in staat LS- en ALS-TTL rechtstreeks aan te sturen. De "ingangsbehoeften" van alle MOS-families zijn dermate bescheiden dat in theorie een zeer hoge fan-out gehaald wordt (zoveel-duizend). In de praktijk treden echter beperkingen op i.v.m. de ingangskapaciteit en de bedradingskapaciteit. Wil men de door de fabrikant opgegeven maximale frekwentie halen (meestal opgegeven bij CL = 10, 15, 50 of 100 pF), dan wordt voor de bepaling van de fan-out CL gedeeld door de ingangskapaciteit. Als vuistregel kan 10 pF per ingang gelden. Merk daarbij op dat de ingangskapaciteit weer sterk afhankelijk is van de toegepaste technologie; CMOS-IC's volgens metal-gate-technologie hebben een grotere ingangskapaciteit dan die volgens Si-gate-technologie. En ook een flink stuk flat-cable of printspoor vormt een behoorlijke kapacitieve belasting. In al deze gevallen is het aan de gebruiker om een nog akseptabele vertragingstijd vast te stellen en daarmee de fan-out.

1) Met 74 en 74LS buffers wordt fan- out 3 × zo groot.

2) 74HC en 74HCT IC's met bus driver outputs hebben een 1,5 × zo hoge fanout.

3) Normaal kan CMOS de sink-current van gewone TTL niet verwerken, maar dit is afhankelijk van merk en type.

4) Theoretisch onbeperkt. In praktijk begrensd door maximaal toegestane vertragingstijden.

5) Normaal geen koppeling mogelijk i.v.m. ongelijke nwo's.

6) Koppeling mogelijk als HC MOS-gedeelte op 3 V werkt.

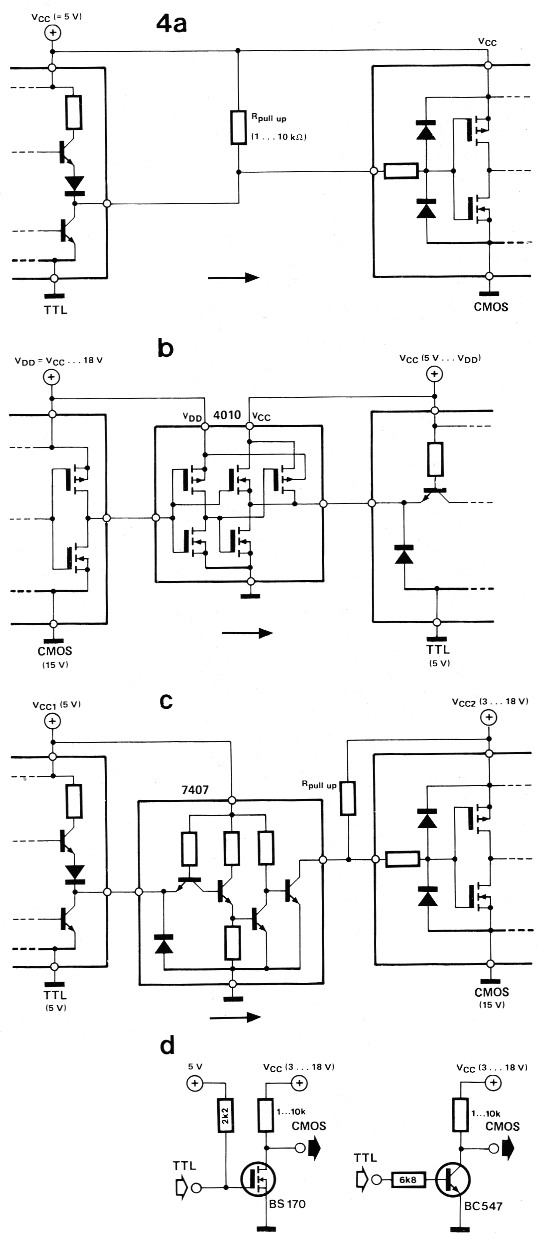

Aanpassingsschakelingen

Om de koppeling van TTL (standaard, LS en ALS) naar 5 V gevoede CMOS en HC-MOS mogelijk te maken, moet ervoor gezorgd worden dat TTL de voor MOS benodigde logische 1 kan leveren (3,5 V min.). Dit gaat eenvoudig door een pull-up-weerstand toe te passen, zoals te zien is in figuur 4. Een kleine waarde is gunstig voor de snelheid; parasitaire kapaciteiten worden dan sneller geladen. De minimale weerstandswaarde wordt begrensd door de maximaal toelaatbare belasting van de betreffende uitgang. Daarbij moet theoretisch ook rekening worden gehouden met het aantal ingangen dat die uitgang al aan te sturen heeft, maar als dat MOS-ingangen zijn, met een verwaarloosbare ingangsstroom, speelt dat geen rol. De minimale weerstandswaarde van de pull-up-weerstand wordt nu:

![]()

De tweede term in de noemer, de som van de ingangsstromen, kan bij MOS-ingangen verwaarloosd worden.

Figuur 4. Diverse nivoaanpassi ngsschakelingen.

4a: van TTL (5 V) naar CMOS (5 V)

4b: van CMOS (op bijv. 15 V) naar TTL (5V)

4c: van TTL (5 V) naar CMOS (op bijv. 15V)

4d: als 4c, maar nu diskreet opgebouwd.

De pull-up-weerstand heeft ook een maximale waarde. Door lekstromen in de uitgang (als bijvoorbeeld meerdere open-kollektoruitgangen met elkaar verbonden zijn) en in de ingangen ontstaat bij een logische 1 een spanningsval over de pull-up-weerstand. De uitgangsspanning mag echter nooit lager worden dan UIH:

![]()

Ook hier kan weer de tweede term in de noemer bij MOS-ingangen verwaarloosd worden.

In de praktijk komt het hierbovenstaande erop neer dat de pull-up-weerstand een waarde van 1 ... 10 kΩ zal hebben. Overigens kunnen die formules ook gebruikt worden bij het dimensioneren van pull-up-weerstanden van open-kollektor-outputs (die al of niet CMOS of HC-MOS aan moet sturen). Anders wordt het als het ene logikagedeelte op een andere voedingsspanning (dus ook met andere logische nivo's) werkt. Een aanpassing van hoog naar laag, bijvoorbeeld van 15 V CMOS naar 5 V TTL, kan gerealiseerd worden met een van de buffers 4009, 4010, 4049 of 4050. Elk huisje bevat zes buffers en die met de nummers 4009 en 4049 zijn inverterend. Behalve voor een aanpassing van hoog nivo naar laag nivo kunnen ze ook gebruikt worden om met CMOS bijvoorbeeld standaard-TTL aan te sturen. De buffers mogen belast worden met 2 TTL-ingangen of 9 LS-TTL-ingangen. De laatste kombinatiemogelijkheid: van 5 V TTL naar "op hoger nivo draaiende" CMOS (of HC-MOS op 6 V). Ook dit is niet zo'n toer als we werken met TTL met openkollektor-outputs. In een aantal gevallen is de UCE van de uitgangstransistor hoger dan VCC. We noemen als voorbeeld de 7406 en de 7407 met 30 V open-kollektor-outputs en de 7416 plus 7417 met 15V openkollektor-outputs (7406 en 7416 zijn inverterende buffers). Verder noemen we nog de 7426 NAND-poort (UCE = 15 V), terwijl uiteraard de mogelijkheid blijft bestaan om een wired-OR-funktie te maken. Bij de dimensionering van de pull-up-weerstand moet er weer op gelet worden dat de sink-stroom (uitgang logisch 0) niet te groot wordt.

De fan-out van de hierboven vermelde 74XX-buffers is 3x de standaard fan-out; de pull-up-weerstand zal dus niet gauw te klein zijn. Daar staat tegenover dat onnodig kleine pull-up-weerstanden resulteren in een groter stroomverbruik bij een te verwaarlozen snelheidswinst.

Het is natuurlijk ook mogelijk met een transistor en twee weerstandjes een diskreet buffertrapje op te bouwen om CMOS met TTL uit te sturen. In wezen kreëer je zo een open-kollektoruitgang. Figuur 4d geeft twee mogelijkheden waarvan de eerste het voordeel heeft van een kleinere schakeltijd.

Tot slot

Bij het werken met TTL is het een (slechte) gewoonte om ongebruikte ingangen vrij te laten zweven. Normaal komt een zwevende ingang overeen met een logische 1. Wordt nu een bepaald LS-TTL-IC met zo'n vrije ingang vervangen door zijn HCT-MOS-ekwivalent, dan krijgen we problemen. De zeer hoge ingangsimpedantie heeft tot gevolg dat het logische nivo niet gedefinieerd zal zijn en de schakeling "doet het niet meer (goed)". Moraal: ongebruikte ingangen altijd op een nivo "vastleggen"; bij TTL met een pull-up-weerstand (1 ... 10 kl-2) naar VCC (LS-ingangen mogen direkt aan +5 V), rechtstreeks aan massa leggen of verbinden met een andere (wel gebruikte) ingang, bij MOS (C-, HC- en HCT-) rechtstreeks verbinden met VCC, massa of een wel gebruikte ingang. De grote diversiteit aan fabrikanten, elk met een reeks logische families, en al die families weer gespecificeerd onder verschillende kondities in verschillende temperatuurgebieden maken het geven van een volledig recept onmogelijk. We geloven dat we voldoende informatie hebben verstrekt om de hobbyist die met de meest courante families werkt de weg te wijzen. In een aantal gevallen zal het altijd nodig blijven de databladen van de betreffende fabrikanten te raadplegen.

| ECL | Emitter Coupled Logic snelle onverzadigde logica. |

| TTL (7400-serie) | Transistor. Transistor Logic, schakelingen met transistoren in verzadiging. Minder snel dan ECL. |

| H-TTL (74H-serie) | High Speed TTL. |

| L-TTL (74L-serie) | Low Power TTL. |

| S-TTL (74S-serie) | Schottky TTL. Door toepassing van Schottky-d ioden worden de transistoren minder ver in de verzadiging gestuurd, waardoor de schakelsnelheid groter wordt. |

| LS-TTL (74LS-serie) | Low Power Schottky TTL. |

| ALS-TTL (74ALS-serie) | Advanced Low Power Schottky TTL. Van de hier besproken typen de snelste en de zuinigste TTL. |

| CMOS (4000-serie) | Complementary Metal Oxide Semiconductor, relatief trage, maar zeer zuinige logicafamilie. |

| HC-MOS (74HC-serie) | High Speed CMOS, CMOS met LS-TTL-schakeltijden. |

| HCT-MOS (74HCT-serie | High Speed CMOS die volledig TTL-kompatibel is, met een geringere vermogensdissipatie als voordeel. |