ACL - nieuwe snelle CMOS-logica

Met de HC- en HCT-familie maakte de CMOSlogica nog niet zo lang geleden een grote stap voorwaarts. Maar deze families konden nog niet alle TTL-families vervangen. Met de nieuwste CMOS-reeks krijgt nu ook de snelste TTL-familie (ALS) een CMOS-konkurrent.

Tot voor kort was het met CMOS nog niet mogelijk om een snelle propagatie-tijd en een hoge fan-out met elkaar te kombineren. Deze kombinatie is echter bij bijvoorbeeld zeer snelle bus- en transmissie-systemen van wezenlijk belang. Vernieuwingen in de CMOStechnologie hebben nu geleid tot de Advanced-CMOS-Logic (ACL). Deze technologie is dus wel snel en heeft een hoge fan-out, maar ook het vermogensverlies bij hoge schakelfrekwenties is verder teruggebracht. En dat is nog niet alles, want ook de gevoeligheid voor elektrostatische ladingen is afgenomen. Een grove vergelijking van ACL met enkele andere logica-families vindt u in tabel 1.

| Vermogensverlies bij f = 1 MHz | propagatie-tijd | storingsmarge bij Ub = 5 V | integratiedichtheid | |

|---|---|---|---|---|

| TTL | middel | kort | klein | gemiddeld |

| CMOS | gering | lang | groot | zeer hoog |

| ECL | hoog | extreem kort | zeer klein | gering |

| I2L | extreem gering | gemiddeld | - | extreem hoog |

| ACL | gering | zeer kort | groot | zeer hoog |

Technologie

ACL-bouwstenen worden in de beproefde silicon-gate-CMOS-technologie gefabriceerd. Er wordt gebruik gemaakt van een standaard 1-mikron-technologie. Verbeteringen in de fabrikage hebben echter geleid tot de verbetering van een aantal eigenschappen. Zo zijn de overgangsweerstanden tussen de aan-sluitpunten op de chip en de buitenwereld kleiner geworden. Kleiner werden ook de interne verbindingen. Verder konden de bij CMOS relatief grote parasitaire kapaciteiten sterk verkleind worden. Alle verbeteringen bij elkaar genomen leidt dat tot snellere logica.

Eigenschappen

De met ACL bereikbare propagatie-tijd is per poort ongeveer 3 ns. Theoretisch zijn dus klokfrekwenties tot zo'n 160 MHz mogelijk. De maximale uitgangsstroom van een poort bedraagt 24 mA! Of de poort die stroom nu moet leveren (source) of afvoeren naar massa (sink), maakt in het geheel niet uit. Het direkt aansturen van LED's, relais, vermogenstransistoren en andere zaken die wat meer stuurvermogen nodig hebben, wordt zo een stuk eenvoudiger.

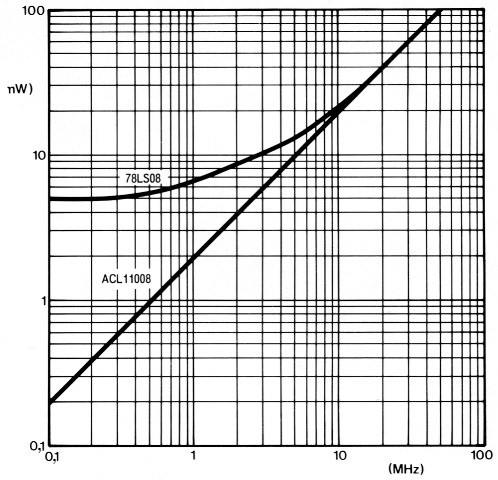

Zoals het een goede CMOS-familie betaamt, is ook bij ACL de vermogensdissipatie zeer gering. Dat maakt het mogelijk een hoge integratie-dichtheid te bereiken en schakelingen met batterijen te voeden. Bovendien ontstaat maar een geringe temperatuurstijging, waardoor de betrouwbaarheid toeneemt. In rust is de vermogensdissipatie van een ACL-poort enkele nano-watt. Uiteraard stijgt de dissipatie bij een toename van de frekwentie, maar bij 1 MHz is de dissipatie nog altijd slechts 1 à 2 mW. In figuur 1 vindt u een vergelijking tussen een ACL- en een LSTTL-AND die bij verschillende frekwenties een kapacitieve belasting van 50 p aansturen.

Figuur 1. flet gedissipeerde vermogen van een ACL- en een LSTTL-IC als funktie van de frekwentie. Alle vier de uitgangen worden gelijktijdig geschakeld en worden belast met 50 pF.

Een andere eigenschap van ACL die gezien mag worden, is de stoor-marge. Bij een geringe belasting (50 µA ofwel 50 CMOS-ingangen) ligt de uitgangsspanning bij een laagnivo beneden 0,1 V en bij een hoog-nivo boven Ub - 0,1 V. Bij de maximale belasting (24 mA) bedragen de worst-case uitgangsnivo's nog altijd slechts 0,5 V en Ub - 0,8 V. Vergelijken we deze waarden met de schakeldrempels van een CMOS-ingang (op 30% en 70% van de voedingsspanning) dan levert een ACL-poort altijd een goed gedefinieerd logisch nivo. Alleen bij de allerlaagste voedingsspanning (circa 2 à 3 V) is het af te raden om een maximaal belaste uitgang ook nog te gebruiken om ingangen van logica te sturen. Bij TTL-kompatibele logica liggen de schakeldrempels op 0,8 en 2 V. liet uitgangssignaal van TTLrkompatibele ACL kan daar dus ruimschoots aan voldoen.

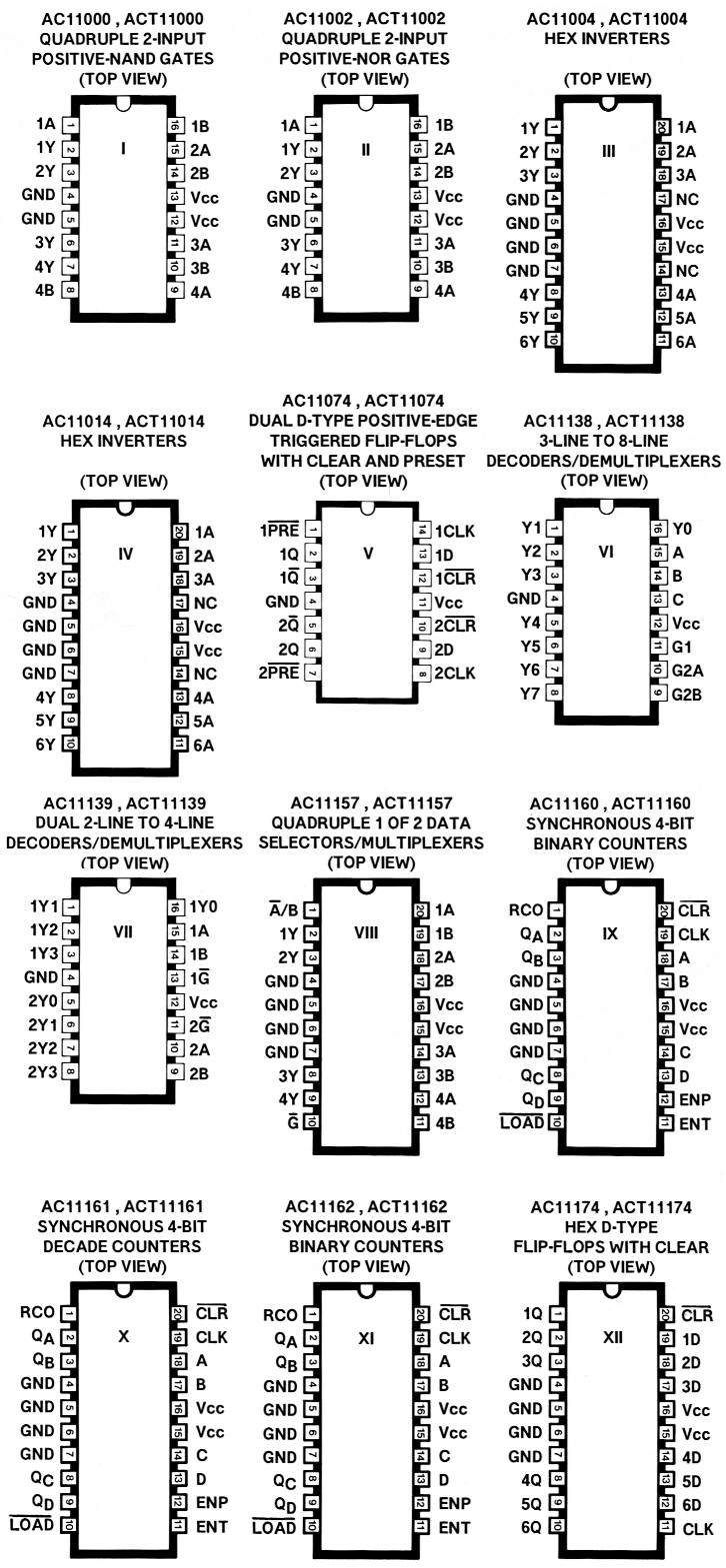

Figuur 3. De aansluitgegevens van enkele belangrijke typen.

Ontwerp-overwegingen

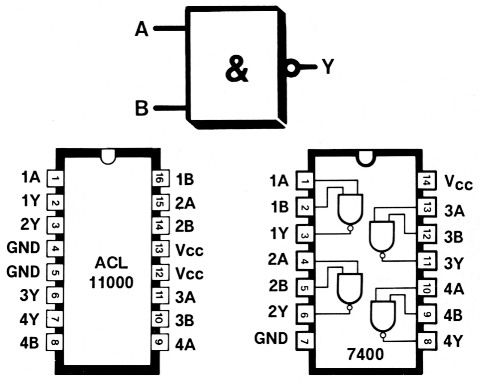

Bij snelle digitale signalen krijgen we eveneens te maken met zeer steile flanken die een extra probleem vormen. Parasitaire reaktanties in de leidingen kunnen gemakkelijk leiden tot reflekties van het signaal in de leidingen, met storingen als gevolg. Om deze problemen in de hand te houden, is afgezien van de pen-kompatibiliteit met de TTL - en CMOS-families. In plaats daarvan is gekozen voor een layout die zoveel mogelijk de lijn van de signaalleidingen volgt (Flow-Trough-Architecture). Deze layout geldt zowel voor de interne struktuur van de IC's als voor de pinning. De opbouw van de IC's ziet er aan de buitenkant als volgt uit: In het midden zitten de voedingsaansluitingen die in veel gevallen uit een aantal parallel geschakelde pennen bestaan. De uitgangen van de poorten zijn aan een zijde van het IC aangebracht en de ingangen aan de andere zijde. De over het algemeen minder frekwent gebruikte stuuringangen worden tenslotte aan de uiteinden van het IC ondergebracht. Deze manier van aansluiten heeft vooral voordelen bij bus-systemen en het gebruik van dubbelzijdige of nog liever multi-layer printen. Het verschil in aansluitgegevens tussen een ACL-IC en een vergelijkbaar TTLIC IC kunt u zien in figuur 2. In figuur 3 is de pinning gegeven van een aantal belangrijke ACL-typen in DIL-behuizing.

Figuur 2. De pinning van ACL is om diverse redenen niet op de gebruikelijke manier uitgevoerd.

Typenummers

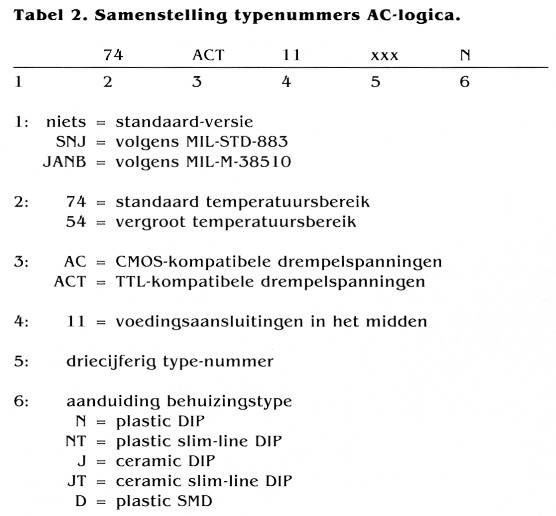

De opbouw van de typenummers voor AC-logica hebben we in tabel 2 op een rijtje gezet. Het eerste onderdeel van het nummer geeft aan of het om een kommercieel of een militair gespecificeerd type gaat. Dan volgt de aanduiding voor het temperatuurbereik (74 of 54). Daarna komt de aanduiding AC of ACT voor respektievelijk CMOS-kompatibele of TTL-kompatibele logica. Vervolgens zien we de aanduiding 11 die aangeeft dat de voedingsaansluitingen in het midden zitten. De laatste drie cijfers vormen het typenummer. Het nummer is altijd driecijferig, maar de nummering is wel hetzelfde als bij HC(T) en TTL. Een 74AC11000 is dus net als een 7400 een viervoudige NAND.

Statische lading

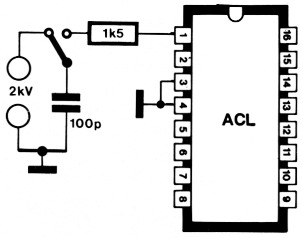

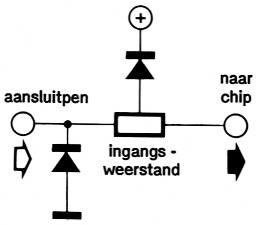

We hebben al vermeld dat ACL niet meer zo gevoelig is voor statische ladingen. Gemeten met een testschakeling volgens figuur 4 verdragen de in- en uitgangen minstens 2 kV met een willekeurige polariteit. De schakeling die voor de beveiliging van de ingangen zorgt, is getekend in figuur 5. De dioden hebben een doorlaatspanning van circa 0,9 V en een zenerspanning van circa 18 V.

Figuur 4. Testschakeling voor het kontroleren uan de beveiliging tegen statische ontladingen.

Figuur 5. ACL-ingangen worden door deze schakeling tegen statische ontladingen beschermd.

De uitgangen worden beschermd door dioden die inherent zijn aan de struktuur van de uitgangstransistoren.

De zojuist genoemde testspanning zegt eigenlijk nog niet zoveel over de bescherming tegen statische ladingen. Minstens zo belangrijk is de energie die met een lading gemoeid is, omdat die immers door het beveiligingscircuit gedissipeerd moet worden.

Omdat het hier om komponenten gaat met zeer geringe afmetingen, is ook het dissipatievermogen beperkt. Uit de meting volgens figuur 4 is uit te rekenen dat ACL-IC's minstens een hoeveelheid energie kunnen verwerken van: W = ½ × C × U2 = ½ × 100p × (2 kV)2 = 0,2 mWs.

Alles bij elkaar

Met ACL hebben we de mogelijkheid gekregen om de voordelen van CMOS ook bij hoge klokfrekwenties te benutten. De nieuwe pinning zal in het begin wel even wennen zijn, maar ze is onontbeerlijk voor het verkrijgen van de gewenste eigenschappen. Een neveneffekt van die pinning is de vereenvoudiging van de print-layout, met name bij multi-layer printen. ACL kan zowel samen met TTL -logica (ACT-typen) als met CMOS-logica (AC-typen) worden ingezet, maar kan ook dienen als volwaardige vervanger. Met name bij nieuwe ontwerpen wordt dit laatste al steeds vaker gedaan. Het ziet er dan ook naar uit dat AC-logica evenals HC-logica snel ingeburgerd zal zijn.

F.P. Zantis.