Ontwerp je eigen chip

prototyping met CPLD's - deel 1

Bij het ontwerpen van een schakeling komen altijd een aantal minder aangename zaken om de hoek kijken: solderen, aansluitingen van chips opzoeken en een wirwar van draden op een print onderbrengen. Dit alles is nu overbodig, aangezien we zelf een digitale schakeling in een CPLD kunnen programmeren.

Eigenschappen experimenteerbord

- CPLD type EPM7128

- JTAG-interface

- Alle I/O-lijnen beschikbaar op boxheaders

- Extra I/O uitschakelbaar via jumpers

- 7-segments display

- 8 LED's

- 8 schakelaars met ontdendercircuit

- on-boord stroomvoorziening

- Eurokoort-formaat

- Uitgebreide ontwikkelomgeving gratis verkrijgboor bij Altera

Het hier gepresenteerde CPLD-experimenteerbord vormt een prima uitgangspunt om direct aan de slag gaan en via het toetsenbord een ontwerp te maken!

Experimenteren met digitale logica roept bij de meeste mensen het beeld op van een gaatjesbord dat compleet is volgestouwd met chips die door middel van ontelbare draadjes met elkaar zijn verbonden. Iedereen die wel eens op deze manier te werk is gegaan, weet dat zoiets meestal vele uren in beslag neemt om te bouwen; en dan willen we nog niet denken aan een eventuele aanpassing indien de schakeling niet meteen de eerste keer werkt.

Als vervanger van zo'n woud van digitale-logica-chips kunnen we een CPLD gebruiken. Deze chips bevatten een heleboel digitale bouwstenen die door programmeren op allerlei manieren met elkaar kunnen worden verbonden. Zo'n chip kan men eigenlijk beschouwen als een moderne variant op een gaatjesprint bezaaid met chips. In plaats van allerlei kleine draadjes solderen kan de ontwerper/onderzoeker nu comfortabel achter de PC de schakeling ontwerpen en in een handomdraai zijn nieuwste ontwerp in deze chip programmeren.

Het mag duidelijk zijn dat dit veel tijd bespaart en als voordeel heeft dat er geen noodzaak is om wijzigingen naderhand op papier of anderszins te documenteren. Men tekent immers (of beschrijft, maar daarover later meer) de schakeling op de computer, waarna de PC wel uitrekent hoe dit ontwerp uiteindelijk in de chip gerealiseerd moet worden.

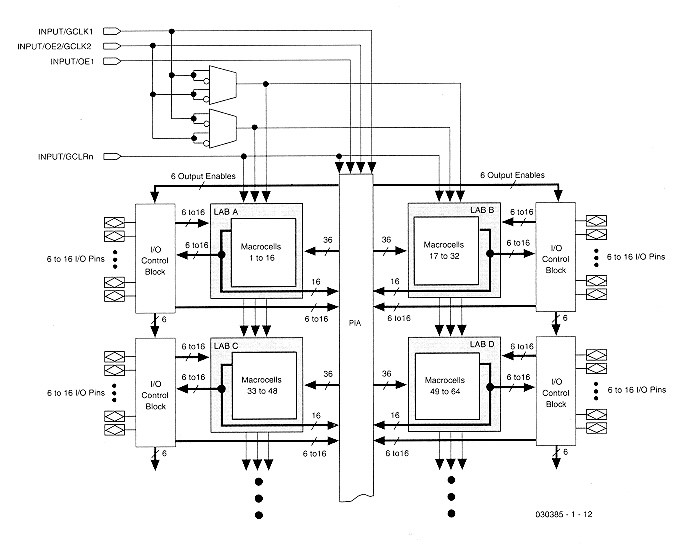

Figuur 1. Globale opbouw van MAX7000-CPLDs.

Ophouw van CPLDs

Bij dit experimenteerbord zijn we uitgegaan van de MAX7000-CPLD's van Altera. De opbouw van deze CPLD's is te zien in figuur 1. Bovenaan in deze figuur vinden we de 4 speciale ingangen voor de CPLD's. Dit zijn signalen die zodanig met de macrocellen zijn verbonden op de chip, dat ze optimaal functioneren in de voor hen bestemde functie (CLK, OE of CLEAR). De ingangen en de uitgangen van de diversen macrocellen worden door de PIA (programmable interconnect array) desgewenst met elkaar verbonden. Verder zijn er ook nog ingangen en uitgangen verbonden met de diverse I/O Control Blocks. Deze hebben als taak het verbinden van de interne signalen met de I/O-aansluitingen van de chip.

In figuur 1 zijn 4 LAB's (Logic Array Blocks) getekend. Deze LAB's bevatten de eigenlijke programmeerbare logica. Iedere LAB bestaat op zijn beurt weer uit 16 macrocellen. De CPLD's in de MAX7000-serie zijn beschikbaar in diverse uitvoeringen, waarbij het typenummer van de chip aangeeft hoeveel macrocellen er in de chip zijn ondergebracht.

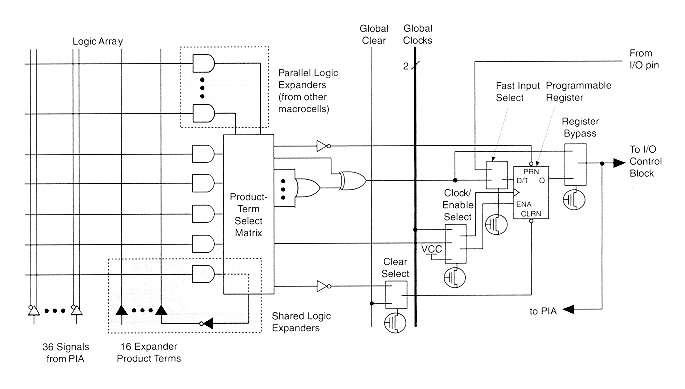

Figuur 2. De opzet van een MAX7000-macrocel.

Macrocel

De macrocel is de plaats waar de feitelijke programmeerbare logica zich bevindt. De opbouw hiervan is te zien in figuur 2. Iedere macrocel heeft een eigen Logic Array dat bestaat uit 36 ingangen die verbonden zijn met een programmeerbare AND-functie. 4 van deze AND-functies worden in de Product Term Select Matrix samengevoegd tot één signaal. Om nu de mogelijkheden van de chip te vergroten is het aantal producttermen nog uit te breiden. Indien u hier meer over wilt weten, verwijzen wij u naar de datasheet van deze CPLD's.

Het signaal dat door de combinatie van AND's en OR's wordt geproduceerd, komt vervolgens terecht bij het register en omliggende logica. Dit gedeelte kan worden gebruikt als D-,T-, JK- of SR-flipflop, of kan zelfs geheel omzeild worden als er geen register nodig is. Gelukkig hoeven we ons als ontwerper niet al te druk te maken hoe we precies ons ontwerp op deze manier kunnen realiseren. Dat is waar de (gratis) software ons te hulp schiet. Maar voordat we ons over de software bekommeren, nemen we het experimenteerbord eerst wat nader onder de loep.

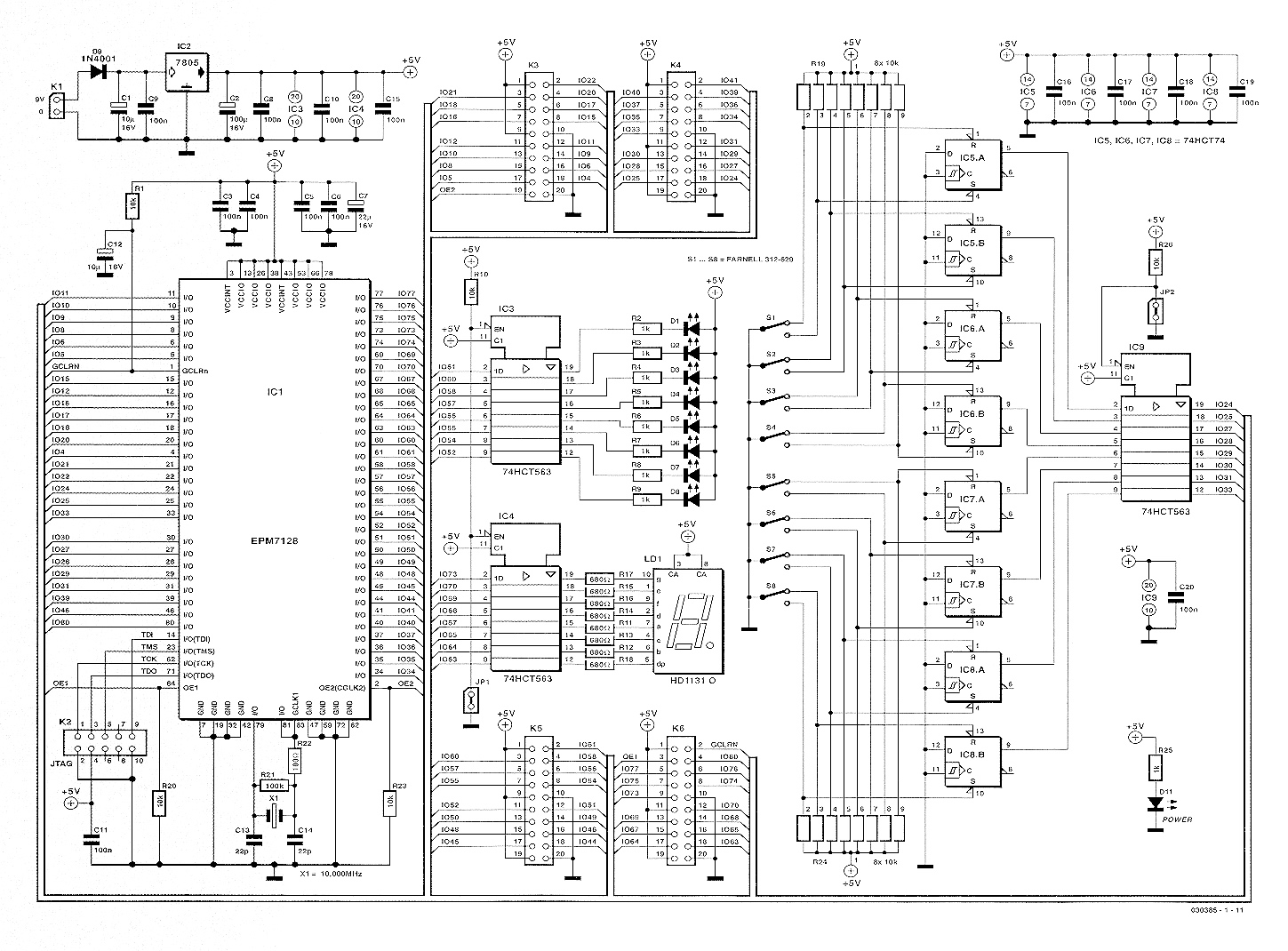

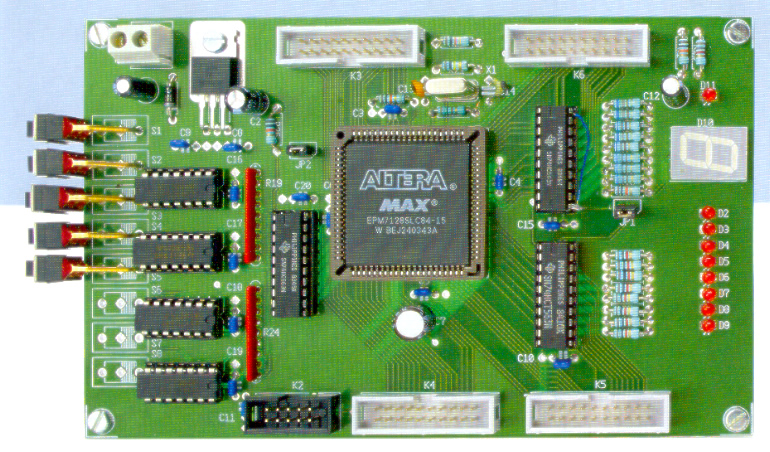

Figuur 3. De schakeling van het experimenteerbord bevat naast de CPLD nog een aantal indicatoren (D1...D8, LD 1) en schakelaars met hardware-ontdendering (S1 ... S8, IC5 ... IC8).

Experimenteerbord

Ons experimenteerbord is redelijk eenvoudig van opzet. Toch bevat het bord meer dangenoeg I/O om de eerste experimenten met CPLD's uit te voeren. Natuurlijk zijn alle relevante aansluitingen van de CPLD via de diverse connectoren naar buiten uitgevoerd, zodat naderhand externe hardware kan samenwerken met dit bord.

Het schema volgens figuur 3 is redelijk simpel. De voedingsspanning van ca. 9 VDC wordt op connector K1 aangeboden. IC2 met omliggende componenten levert dan de voedingsspanning van 5 V voor de hele schakeling. LED D11 en R25 zorgen voor de spanningsindicatie.

De CPLD is hier als IC1 in het schema getekend. De JTAG-programmeerinterface is via K2 naar buiten uitgevoerd. De pen-layout van deze connector is compatibel met de Byte-Blaster van Altera en is dus ook compatibel met de Parallel-JTAG-interface van Elektuur (zie halfgeleidergids 2002, pag. 44). Het reset-circuit wordt door het RC-netwerk R1/C12 gevormd. Ten slotte is met behulp van R21, R22, C13, C14 en X1 een oscillator gerealiseerd. Hoe we hier in combinatie met de CPLD een oscillator van kunnen maken, zal bij de voorbeelden aan bod komen.

Op iedere experimenteerprint mag wat simpele I/O niet ontbreken. IC3 is een buffer die enkele signalen van de CPLD versterkt en daarmee de LED's D1 t/m D8 aanstuurt. IC4 doet iets soortgelijks voor de aansturing van een 7-segments display. Indien deze I/O niet gewenst is, kan deze van de CPLD worden losgekoppeld door jumper JP1 te verwijderen.

Als ingang hebben we gekozen voor 8 schakelaars. Om het experimenteren in het begin niet al te moeilijk te maken, zijn deze 8 schakelaars (S1 t/m S8) voorzien van een ontdender-circuit. Hiervoor zijn IC5...IC8 verantwoordelijk. Deze ingangen zijn via IC9 verbonden met de CPLD, maar ook hier is weer de mogelijkheid open gelaten om deze schakeling van de CPLD los te koppelen. In dit geval is JP2 daarvoor verantwoordelijk.

Connectoren K3...K6 bieden tenslotte alle relevante signalen van de CPLD aan de buitenwereld aan.

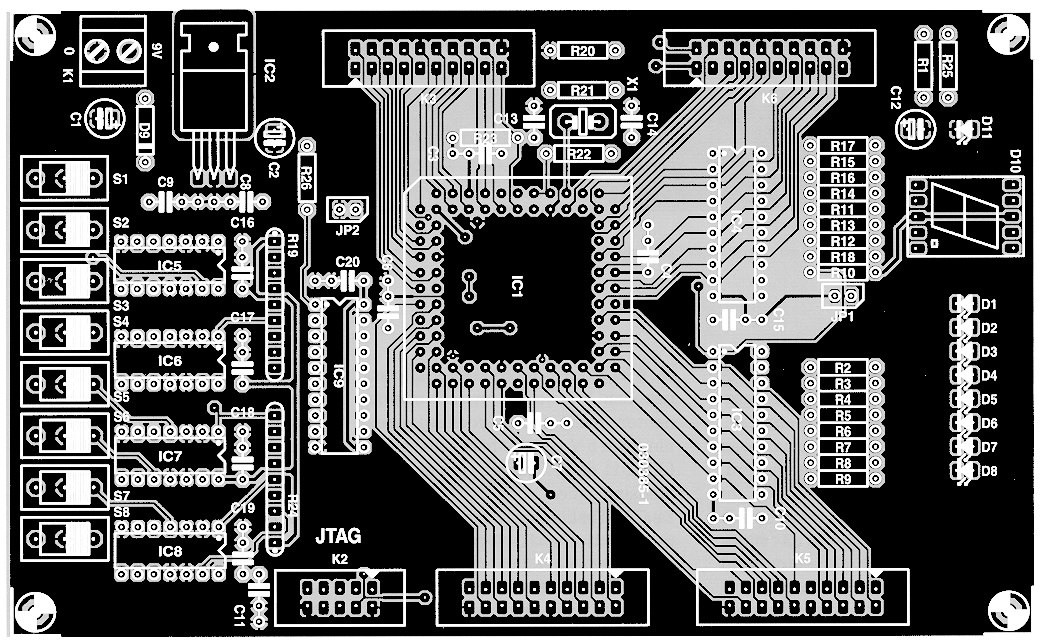

Figuur 4. Componentenopstelling van de dubbelzijdige experimenteerprint. De bijbehorende layouts zijn te vinden achterin deze uitgave op de layout-pogina's.

Bouwen

De dubbelzijdige print die in figuur 4 is afgebeeld, is royaal van opzet om alles goed toegankelijk te houden. Alle connectoren zijn aan de zijkanten van de print geplaatst. De montage van de componentenopbouw van de print is zeker geen moeilijke klus. Wie in CPLD's is geïnteresseerd, zal zeker wel eens eerder een print hebben opgebouwd. Bij het monteren van de onderdelen dient u vooral op een juiste oriëntatie bij de IC's, LED's en elco's te letten. Voor de IC's zijn voetjes zeker aan te bevelen, voor de CPLD is een bijpassende 84-pens PLCC-voet noodzaak. Let op dat de afgeplatte hoek van het PLCC-voetje op de juiste plaats op de print komt te zitten (zie componentenopdruk!), want die kan ook verkeerd in de printgaatjes gestopt worden. De CPLD past overigens maar op één manier in het voetje. Delen van de schakeling die niet gebruikt worden, kunnen worden losgekoppeld van de CPLD door middel van jumper JP1 en JP2. Maar u kunt die delen natuurlijk ook niet monteren. Zo kan IC4 met LD1 en R11...R18 worden weggelaten als het zevensegment-display niet nodig is. Hetzelfde geldt voor IC3 met D1...D8 en R2...R9, als geen LED-indicatoren nodig zijn. Bij de schakelaars hoeven alleen de exemplaren te worden geplaatst die voor de eerste experimenten nodig zijn.

De spanningsstabilisator (IC2) wordt plat op de print gemonteerd en met een boutje en moertje vastgezet. Een extra koelvin is niet nodig, als extra aangesloten hardware tenminste niet te veel stroom vraagt.

De voedingsspanning kan worden verzorgd door een netadapter die circa 9...15 V levert bij minimaal 100 mA. Deze waarde geldt voor de experimenteerprint zelf, daarbij komt nog de stroom die eventuele extra hardware nodig heeft.

Figuur 5. Op deze foto van een opgebouwd prototype is te zien dat schakelaars naar behoefte kunnen worden gemonteerd; hier zijn er vijf geplaatst.

Software

Het programmeren van de CPLD vereist PC-software om de benodigde programmeerbestanden aan te maken en deze uiteindelijk in de chip zelf te programmeren. Gelukkig heeft de fabrikant van de CPLD hier een mooi (en gratis) software-pakket voor. De software heeft de naam Quartus en kan van de website van de fabrikant worden gedownload.

Vanaf de beginpagina van deze website kiest u voor de rubriek Design Software, te vinden onder het hoofdstuk Products. In het nieuwe venster kiest u dan Quartus II Web Edition. Volg hierna de instructies die op het scherm verschijnen. Let wel op de grootte van de download. Het bestand is maar liefst 144,9 MB groot, dus als u gebruik maakt van een telefoonverbinding is het misschien handiger om dit bestand bij iemand met een snellere Internet-verbinding te downloaden!

Na het installeren van de software moet u nog een gratis licensie aanvragen. Hoe dit precies in zijn werk gaat wordt op de website van Altera duidelijk uitgelegd.

Volgende maand

De volgende maand zullen we aan de hand van een aantal voorbeelden uitleggen hoe u in Quartus een schakeling kunt ontwerpen en uiteraard deze voorbeelden op het experimenteerbord kunt uitproberen. Voor het programmeren is naast dit experimenteerbord ook nog een JTAG-interface nodig, zoals de reeds genoemde Parallel-JTAG-interface uit de Halfgeleidersgids 2002 van Elektuur.

Het is aan te raden om in afwachting van het volgende nummer al eens de tutorial van Quartus te bekijken. Deze is te vinden onder het menu 'Help'. Met behulp van deze tutorial kunt u alvast vertrouwd raken met de opbouw van de software en de mogelijkheden van de software bekijken.

Onderdelenlijst

Weerstanden:

R1,R10,R2O,R23,R26 = 1O k

R2...R9,R25 = 1 k

R11...R18 = 680 Ω

R19,R24 = weerstand-array 8 x 10 k

R21 = 100 k

R22 = 100 Ω

Condensotoren:

C1,C12 = 10 µ/16 V radiaal

C2 = 100 µ/16 V radiaal

C3...C6,C8...C11,C15...C20 = 100n

C7 = 29 µ/16 V radiaal

C13,C14 = 22 p

Halfgeleiders:

D1...D8,D10 = LED rood, low current

D9 = 1N4001

LD1 = 7-segment-display CA (bijv. HD1131 O)

IC1 = EPM7128SLC84-10 of EPM71285LC84-15

IC2 = 7805

IC3,lC4,IC9 = 74HCT563

IC5...IC8 = 74HCT74

Diversen:

JP1,JP2 = 2-polige header met jumper

K1 = 2-polige printkroonsteen, steek 5 mm

K2 = 2x5-polige boxheader

K3...K6 = 2x10-polige boxheader

S1...S8 = schuifschakelaar 1 x wissel, bijv APEM A2

X1 = kristal 4,000 MHz

84-pens PLCC-voet

print EPS 030385-1

Print is ook beschikbaar op www.elektor.nl en op de extra layoutpagina's achterin deze uitgave.

Wordt vervolgd.