Direct Digital Synthesizer (DDS)

In letzter Zeit hört man öfters den Begriff "Direktsynthesizer" oder einfach die Abkürzung "DDS", was meist als Highlight in Werbeanzeigen von Transceivern der oberen Preisklasse erscheint.

Dieser Beitrag erläutert die wesentlichen Unterschiede zwischen PLL und DDS und soll das faszinierend einfache Funktionsprinzip der direkten Frequenz-synthese mit Hilfe einer Rechnersimulation erklären.

Die wichtigsten Unterschiede zwischen der indirekten Frequenzsynthese mit klassischem PLL-geregeltem Oszillator und der Frequenzerzeugung durch Direktsynthese sind folgende:

Der DDS benötigt keinen Oszillator, der die Ausgangsfrequenz erzeugt. Die Taktfrequenz ist gleichzeitig auch die Referenz des DDS und damit die höchste vorkommende Frequenz. Bei der PLL ist die Referenzfrequenz die kleinste vorkommende Frequenz.

Der Ausgangsfrequenzbereich des DDS kann je nach Auflösung nahezu beliebig viele Oktaven überstreichen. Die kleinstmögliche Frequenz ist die Taktfrequenz dividiert durch die größte Zahl, die mit der binären Eingabe darstellbar ist. Die größtmögliche Frequenz beträgt nach dem Shannonschen Abtasttheorem 50% der Taktfrequenz, liegt aber in der Praxis wegen der endlichen Steilheit von nachgeschalteten Tiefpaßfiltern bei etwa 40% der Taktfrequenz.

Bei herkömmlichen PLLs wird der Frequenzbereich durch den Ziehbereich des verwendeten Oszillators begrenzt.

Die Einrastzeit des DDS wird praktisch nur noch von den Gatterlaufzeiten bestimmt, während beim PLL-stabilisierten Oszillator das vergleichsweise sehr träge Einschwingverhalten weitestgehend vom Schleifenfilter bestimmt wird.

Steht eine rauscharme Takt-Referenzfrequenz zur Verfügung, weist das Seitenbandrauschen des DDS in Trägernähe hervorragende Werte auf, die von herkömmlichen Oszillatoren kaum erreichbar sind. Bei "krummen" Teilerverhältnissen, also wenn die Division aus Takt- zu Ausgangsfrequenz einen Rest ergibt, treten beim DDS jedoch mehr oder weniger starke nichtharmonische Frequenzen auf. Diese Störungen werden aber um so geringer, je tiefer die Ausgangsfrequenz gegenüber der Taktfrequenz ist.

Beim PLL-Oszillator treten normalerweise außer den beherrschbaren Nebenschwingungen im Abstand der Referenzfrequenz keine nichtharmonischen auf. Das Seitenbandrauschen eines PLL-Oszillators läßt sich für spezielle Aufgaben durch geeignete Dimensionierung vom Schleifenfilter, Referenzfrequenz und Teilerverhältnissen ebenfalls weitgehend unterdrücken.

Für den professionellen DDS-Chip SP 2001 von Plessey werden folgende Daten genannt: Die Einstellzeit für jede beliebige Frequenz zwischen 5 kHz und 100 MHz beträgt weniger als 17 Nanosekunden. Das Seitenbandrauschen in ± 25 kHz vom Träger ist besser als -135 dBc/Hz.

Die Unterdrückung nichtharmonischer Frequenzen beträgt bei 100 MHz -32 dBc und verbessert sich bei kleineren Frequenzen bis etwa -46 dBc. Die maximale Taktfrequenz liegt bei 350 MHz, die Auflösung bei 16 Bit, womit für 5-kHz-Schritte eine Taktfrequenz von 327,68 MHz benötigt wird.

Der nicht gerade amateurfreundliche Preis von etwa 600 bis 800 DM pro Stück ist hoffentlich nur eine vorübergehende Erscheinung, da der Hersteller nur eine kleine Serie aufgelegt hat. 1990 soll aber eine größere Serie mit noch besseren Daten lieferbar sein.

Der 32-Bit-DDS-Phase-Accumulator-Chip 10G102 der Firma GigaBit Logic mit 1 GHz Taktfrequenz liegt bei über 1000 DM, dafür lassen sich 0,25-Hz-Schritte durchgehend von 0,25 Hz bis ins 70-cmBand realisieren.

Das DDS-Prinzip

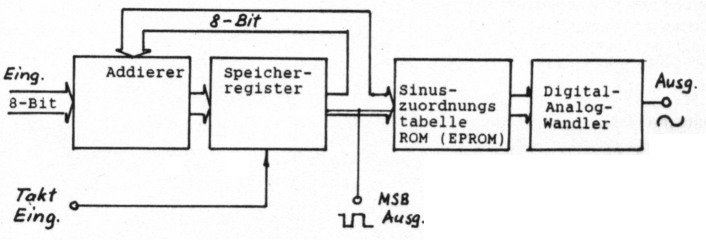

Abb.1: Prinzip eines DDS mit digitaler Sinuserzeugung.

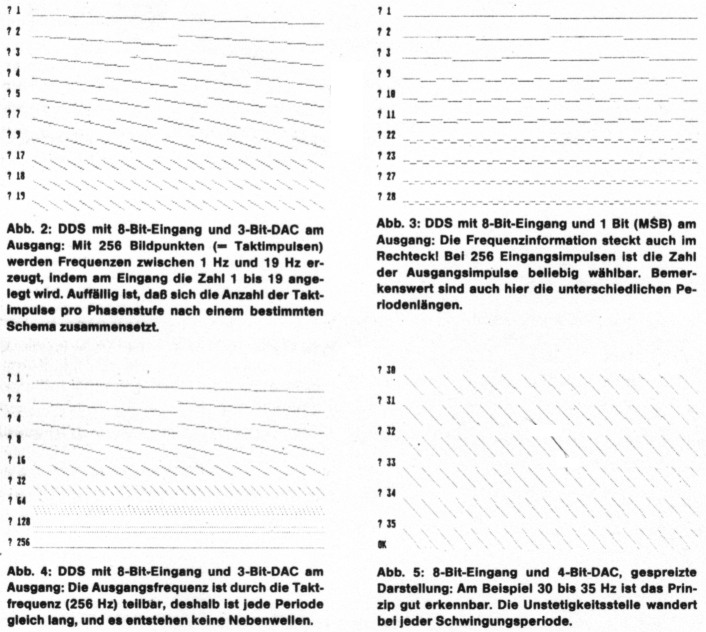

Am Beispiel eines 8-Bit-DDS läßt sich das Funktionsprinzip sehr anschaulich darstellen. Mit einer fest vorgegebenen Taktfrequenz von 256 Hz lassen sich Ausgangsfrequenzen von 1 Hz bis etwa 100 Hz in 1-Hz-Stufen erzeugen. Bei der graphischen Darstellung auf einem PC-Bildschirm entspricht jeder Punkt einer positiven Halbwelle der Taktfrequenz.

Das Kernstück unserer DDS-Nachbildung besteht aus einem binären 8-Bit-Addierer mit einem 8-Bit-Speicherregister am Ausgang. Beim ersten Taktimpuls wird das Eingangs-Datenbyte zum Speicherinhalt Null addiert. Im Speicher steht jetzt das am Eingang anliegende Datenbyte. Bei jedem weiteren Taktimpuls wird zum Speicherinhalt wieder das Eingangsdatenbyte addiert. Die Bits, aus denen sich das Datenwort im Speicher zusammensetzt, enthalten acht Phaseninformationen einer Schwingungsperiode der Ausgangsfrequenz.

Der aus Addierer und Speicher bestehende Baustein wird in Datenblättern auch "DDS Phase Accumulator" genannt. Ist der Speicher voll, wird der übertrag abgeschnitten und geht verloren. Die 8-BitAddition, die bei jedem Takt erfolgt, läuft aber weiter. Jeder Takt addiert also die Eingangsdaten zu einem Rest im Speicher und hinterläßt der darauffolgenden Addition einen neuen, meist anderen Rest.

Die so gewonnene Phaseninformation der Ausgangsfrequenz entspricht genau dem Verhältnis aus angelegtem Eingangs-Datenwort zur Speichergröße multipliziert mit der Taktfrequenz. Wird zum Beispiel am Dateneingang, der auch mit "Frequency Set" oder "Frequency Word" bezeichnet wird, die binär codierte Zahl 17 beschaltet, beträgt die Ausgangsfrequenz genau 17 Hz, wenn die Taktfrequenz 256 Hz ist.

Die Phaseninformation steht zwar bei jedem Taktimpuls mit 8 Bit Breite zur Verfügung; zur Erzeugung rechteckförmiger Ausgangsfrequenzen zur digitalen Weiterverarbeitung reicht aber bereits ein Bit aus. Die Ausgangsfrequenz des DDS vermag viele Oktaven zu überstreichen. Um eine oberwellen- und nebenwellenarme Ausgangsfrequenz zu erhalten, benutzt man mehrere Bits, jeweils beim MSB angefangen, die in einem ROM "Look Up Table" genannt, so zugeordnet werden, daß ein nachgeschalteter Digital-AnalogWandler (DAC) ein treppenförmig zusammengesetztes Sinussignal liefert.

Bei unserem Beispiel benutzen wir die drei höchstwertigen Bits, um eine achtstufige Sägezahnspannung zu erzeugen. Der Einfachheit halber wird hier auf die Sinuserzeugung verzichtet. Professionelle DDS nutzen für die Phaseninformation 8 bis 12 Bits bei einem bis zu 32 Bit breite "Phase Accumulator", wenn kleine Frequenz-schritte benötigt werden.

Die Unterdrückung nichtharmonischer Frequenzen steigt mit dem Verhältnis zwischen Takt zu Ausgangsfrequenz, nicht aber mit der Breite des "DDS-Phase-Accumulators", weil jeder Taktimpuls nur eine Berechnung der Ausgangsdaten liefern kann.

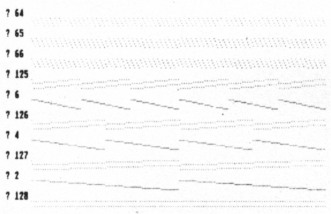

Abb. 6: DDS mit 8-Bit-Eingang und 3-Bit-DAC am Ausgang: Bei Frequenzen über 32 Hz können in elner Periode die acht Stufen des 3-Bit-DACs nicht mehr dargestellt werden. Die Phaseninformation geht aber nicht verloren, sondern wird in die nächste Schwingungsperiode übertragen. Nahe am theoretischen Grenzwert von 128 Hz wird die Phaseninformation wieder in Form einer Schwebung sichtbar. Bel 128 Hz wird Jede Schwingung nur noch durch zwei Pegelzustände dargestellt.

Die DDS-Computersimulation

Was mit Worten nur schwer erklärbar ist, kann anschaulicher mit der Graphik eines kleinen Omikron-Basic-Programmes auf dem Atari-1040 ST gezeigt werden. Die hier gewählte Darstellung und Berechnung erfolgt wegen der besseren übersicht im Dezimalsystem, obwohl ein echter DDS natürlich nur binäre Daten verarbeitet.

Mit INPUT E wird eine beliebige ganzzahlige Frequenz vorgegeben, die zwischen 1 Hz und etwa 100 Hz liegt, bei einer angenommenen konstanten Taktfrequenz von 256 Hz. Das Programm stellt pro Bildschirmzeile 256 Perioden der Taktfrequenz mit 512 Pixel dar; es laufen also in der "FOR X...NEXT X"-Schleife 256 Additionen ab. S ist die Variable für den Speicherinhalt, der anfangs Null ist. Die Akkumulatorfunktion wird durch S: = S + E nachgebildet. Das Abschneiden des nicht mehr benötigten überlauf-Bits bzw. das Anwachsen des Speicherinhaltes auf über 256 verhindert der MOD-Befehl, der vom Speicherinhalt solange 256 subtrahiert, bis sein Inhalt kleiner als 256 ist.

Die Amplitude der Ausgangsfrequenz wird durch die Variable Y gebildet. Die drei höchstwertigen Bits ermöglichen es, die momentanen Amplitudenwerte bei acht gleichen Phasenänderungen pro Periode auszugeben. In der Programmzeile Y = INT (S/32) werden die fünf niederwertigsten Bits abgeschnitten. Die verbleibenden drei Bits simulieren die Ausgangsspannung eines 3-Bit-Digital-AnalogWandlers (DAC).

DOS mit 8-Bit Eingang und 3-Bit DAC am Ausgang: 100 CLS : REM NAME: *** DDS --SIMULATION 110 FOR L=1 TO 10: REM SCHLEIFE FR 10 KURVEN 120 PRINT 130 INPUT E: REM EINGABE DER FREQUENZ / HZ 140 IF E=0 THEN END : REM ABBRUCH BEI EINGABE 0 150 S=0: REM SPEICHER RESET 160 FOR X=0 TO 255: REM TAKT IMPULSE 170 S= (S MOD 256): REM SCHNEIDET UEBERLAUF AB 180 Y= INT(S/32): REM SCHNEIDET LSB AB 190 Y=2*Y+32*L: REM ZEILENVORSCHUB 200 DRAW 2*X+45,Y: REM GRAFIK BILDSCHIRM 210 S=S+E: REM ACCUMULATOR 220 NEXT X: REM NAECHSTER TAKTIMPULS 230 NEXT L: REM NAECHSTE KURVE 240 END

Abb. 7: Das Basic-Programm.

Wenn das rechteckförmige Ausgangssignal direkt am MSB des "Phase Accumulators" betrachtet werden soll, müssen die sieben niederwertigsten Bits abgeschnitten werden, indem die Zeile in Y = INT (S/128) umgestellt wird.

Auf die Simulation des "Look Up Table", also des ROMs oder EPROMs mit der Zuordnungstabelle zur Erzeugung eines Sinusfunktion aus der Sägezahnfunktion, wird hier verzichtet, weil sie zum Verständnis des DDS-Prinzips nichts beiträgt und das Basic-Programm nur unnötig verlängert. Die übrigen Programmzeilen dienen nur dazu, mehrere "Frequenzeinstellungen" auf dem Bildschirm abzubilden. Es werden pro Frequenzdarstellung 512 Bildpunkte im Graphikmodus belegt; ein Taktimpuls besteht demnach aus einem "schwarzen" und einem "weißen" Bildpunkt.

Die amateurmäßige Nutzung des DOS

Professionelle DDS-ICs scheiden zur Zeit aus Kostengründen noch aus. Verzichtet man auf teuere hochintegrierte GaAs- und VHSICs (Very High Speed Integrated Circuit) mit Taktfrequenzen im UHF- oder GHz-Bereich, bleiben dem innovativen Funkamateur dennoch verschiedene Möglichkeiten.

Beispielsweise lassen sich mit einem 20 Bit breiten DDS-Phase-Accu bei einer Taktfrequenz von 10,48576 MHz 10-HzSchritte von 10 Hz durchgehend bis etwa 4 MHz realisieren. Damit ist beispielsweise ein DDS-VFO mit 0 bis 4 MHz Durchstimmbereich realisierbar. Es muß allerdings geprüft werden, ob die jeweils benötigte Nebenwellenunterdrückung mit dem DDS erreicht werden kann. Schnelle TTL-ICs reichen zur Realisierung aus.

Die digitale Sinus-Frequenzerzeugung besteht aus einer "Look Up Table", die in einem EPROM abgelegt sein kann, und aus einem 8-Bit-Digital-Analog-Wandler mit nachgeschaltetem Tiefpaßfilter und Pufferverstärker. Für höhere Ansprüche empfiehlt sich der Selbstbau eines "DOSPhase-Accumulators" mit acht Stück 4Bit-Addierer 74F285 (Valvo), zusammen geschaltet mit dem "32-Bit-Look-Ahead Carry Generator" 74F882 zur Steigerung der Ubertragsgeschwindigkeit und vier Stück 8-fach-"Latch/Flip-Flops" 74FS74. Man erhält damit einen DOS mit 32 Bit breitem Eingangsregister.

Bei einer Taktfrequenz von 42,949673 MHz aus einem Quarzoszillator ergibt sich eine Auflösung von 0,01 Hz (!) bei einer Ausgangsfrequenz bis etwa 17 MHz. Die Schaltung wurde aber noch nicht aufgebaut; wahrscheinlich funktionieren die ICs auch noch bei der doppelten Taktfrequenz, wo sich bei einer Auflösung von 0,02 Hz Ausgangsfrequenzen von über 30 MHz erzeugen lassen. Die Kosten für einen Satz ICs des Direktsynthesizers liegen bei etwa 100 DM.

Praktische Versuche mit Eigenbau-DDS wurden noch nicht durchgeführt.

Zusammenfassung

- Der DDS eignet sich hervorragend zur Hilfsfrequenzerzeugung in Frequenzaufbereitungen.

- Bei jedem Taktimpuls läuft eine vollständige Berechnung der Phasendaten zur Erzeugung der Ausgangsfrequenz ab.

- Der DDS benötigt zur Erzeugung hoher Frequenzen sehr schnelle, teure Bausteine.

- Die kleinste Schrittweite der Ausgangsfrequenz hängt nur von der Breite des Eingangsregisters ab.

- Es können mit entsprechendem Aufwand Frequenzen vom Millihertz-bis in den UHF-Bereich nahezu stufenlos erzeugt werden.

- Am Ausgang des DDS treten unerwünschte nichtharmonische Nebenschwingungen auf, die vom Verhältnis zwischen Takt- und Ausgangsfrequenz abhängen.

- Die sinusförmige Ausgangsfrequenz wird digital mit Hilfe eines ROMs (Look Up Table) kombiniert mit einem Digital-Analog-Wandler (DAC) mit nachgeschaltetem Tiefpaß erzeugt.

- Die rechteckförmige Ausgangsfrequenz kann ohne Look Up Table und DAC direkt am MSB des DDS-Phase-Accumulators abgenommen werden.

Literatur

- Integrierte FAST-Schaltungen. Valvo Datenbuch 86.

- Plessey Datenblatt SP 2001.

- GigaBit Logic Datenblatt 32-Bit DDS-Phase Accumulator 10G102.

DK8UT, Gerhard Pleier.