10-MHz-Zeitbasis für Frequenzzähler, mit PLL für DCF77

Wenn man die Frequenz eines HF-Signals genau bestimmen möchte und mit verschiedenen Frequenzzählern mißt, so erhält man erfahrungsgemäß entsprechend viele verschiedene Anzeigewerte, da die Zeitbasen meist von der Sollfrequenz abweichen. Um dem abzuhelfen, wurde die 10-MHz-Referenz zum Prüfen und Abgleichen der Zeitbasis von Zählern entwickelt. Die Frequenz ist über eine Phasenregelschleife mit dem 6,2-MHzSignal des DCF77-Empfängers aus Heft 1/1984 (1) verkoppelt, so daß eine ausreichend genaue Referenz zur Verfügung steht.

Der Oszillator der Zeitbasis eines digitalen Frequenzzählers sollte möglichst exakt und auch langzeitstabil mit der Sollfrequenz schwingen, da jede Abweichung einen entsprechend großen relativen Fehler in der Anzeige zur Folge hat. Deshalb ist ein hochwertiger Oszillator, möglichst ein temperaturkompensierter Quarzoszillator (TCXO) oder noch besser ein temperaturgeregelter Oszillator (OCXO) erforderlich.

Zum Ausgleich der Langzeitdrift der Frequenz durch Alterung ist eine von einer Normalfrequenz abgeleitete Regelung wünschenswert.

Mit dem in (1) beschriebenen DCF77-Empfänger steht ein Referenzsignal zur Verfügung, mit dem eine solche Frequenznachführung mit verhältnismäßig einfachen Mitteln möglich ist.

In der im folgenden beschriebenen Baugruppe wird ein industriell gefertigter Oszillator verwendet, und zwar ein temperaturkompensierter 10-MHz-Quarzoszillator (TCXO) mit Frequenz-Feinabgleich durch eine Kapazität, der bereits ungeregelt eine gute Zeitbasis darstellt. Damit ist auch bei Ausfall des DCF77-Referenzsignals noch eine recht genaue Frequenz gegeben.

Die Frequenznachführung erfolgt über einen Phasenregelkreis (PLL), und als Referenz-signal wird das 6,2-MHz-Signal, gegebenenfalls das 3,1-MHz-Signal, aus dem DCF77-Empfänger verwendet.

Da die Baugruppe als Zeitbasis für digitale Schaltungen gedacht ist, liefert der Ausgang das 10-MHz-Signal mit TTL-Pegel. Es kann über dekadische Teiler bis auf 1 Hz geteilt werden. Durch Verwendung von Teilern durch 5 und durch 2 stehen dann sämtliche dekadischen Frequenzen von 10 MHz bis 1 Hz, und Zwischenwerte 5 MHz, 500 kHz usw. bis 5 Hz mit TTL-Pegel für andere Zwecke zur Verfügung.

Durch die Möglichkeit des Zurücksetzens der 6 niederfrequenten Teilerdekaden, lassen sich die Schalt- und Steuersignale für einen Digitalzähler leicht erzeugen.

1. Schaltungsbeschreibung

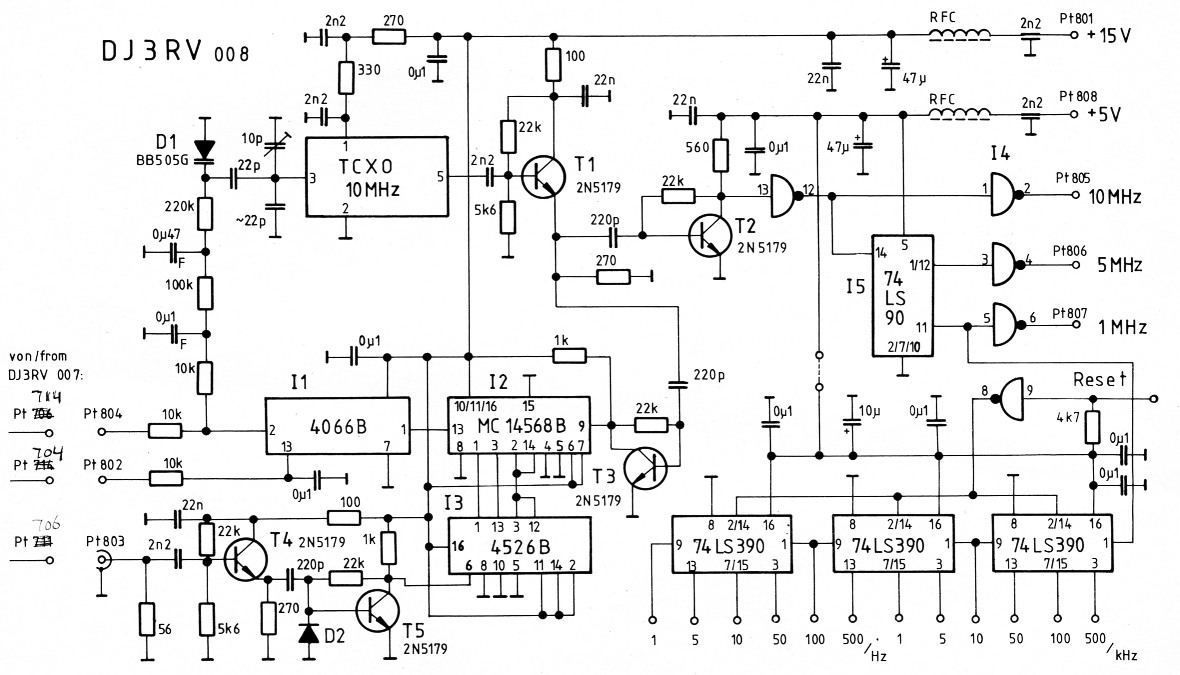

Wie die Schaltung in Bild 1 zeigt, liefert ein temperaturkompensierter Quarzoszillator (TCXO) das 10-MHz-Signal, dessen Frequenz durch eine variable Kapazität gezogen werden kann. Diese Ziehkapazität, nach Herstellerangabe 27 pF, wird durch eine Festkapazität, einen 10-pF-Trimmer zum Feinabgleich, und die Kapazitätsdiode D1 zur Frequenzregelung gebildet.

Bild 1: Schaltung der 10-MHz-Baugruppe mit Teilerprogramierung für ein 6,2-MHz-Referenzsignal.

Die Frequenzregelung mit dem Phasenkomparator I2 ist ähnlich der schon in der Baugruppe DJ3RV 007(1) verwendeten. Das 10-MHz-Ausgangssignal des TCXO wird über T1 als Pufferverstärker und Impedanzwandler mit dem Pegelwandler T3 auf CMOSPegel verstärkt und mit dem Teiler in 12 geteilt. Der Teilerfaktor beträgt 100 und ist durch Pin 10 und 11 auf "high" fest programmiert.

Das 6,2-MHz-Referenzsignal aus der Baugruppe DJ3RV 007 wird am Anschlußpunkt Pt803 eingespeist, und mit T4 und T5 auf CMOS-Pegel verstärkt. I und der zweite programmierbare Teiler in I2 teilen dieses Signal durch 62 und führen es dem Phasenkomparator zu .

Leider zeigt sich, daß nicht alle CMOS-Teiler bei 6,2 MHz sicher durch 62 teilen. Es wird daher im nächsten Kapitel auf die Möglichkeiten hingewiesen, ein 3,1-MHz-Signal einzuspeisen und dieses durch 31 zu teilen.

Der Phasenkomparator führt den Phasenvergleich bei 100 kHz durch, und am Tri-State-Ausgang I2/Pin 13 liegt das Regelungssignal an. Über einen Schalter I1 kann dieses Signal bei Senderausfall des DCF abgeschaltet werden. Die Schaltspannung wird am Pt802 eingespeist und ebenfalls von der Baugruppe DJ3RV 007 geliefert. Dann liegen an der Diode D1 die an Pt804 eingespeisten hochstabilen 5 V, ebenfalls aus DJ3RV 007.

Das 10-MHz-Signal wird über T1 und T2 auf TTL-Pegel verstärkt, und über Inverter aus I4 mit TTL-Pegel an Pt 805 rückwirkungsarm ausgekoppelt. Der Teiler I5 teilt durch 2 und 5, so daß am Pt806 ein 5-MHz-Signal und am Pt807 ein 1-MHz-Signal auskoppelbar sind.

Auf der Platine ist noch eine weitere Teiler-kette aus 6 dekadischen Teilern vorgesehen, so daß Signale bis 1 Hz zur Verfügung stehen. Diese Teilerkette läßt sich mit dem "Reset" zurücksetzen, anhalten und definiert starten, so daß damit die Steuersignale für einen Frëquenzzähler erzeugt werden können.

2. Aufbauhinweise

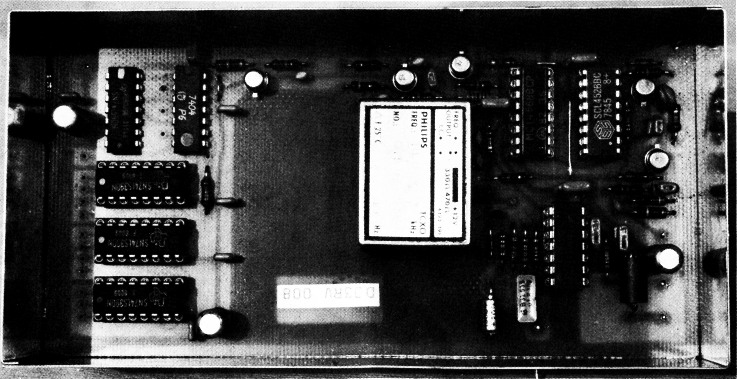

Die Schaltung ist auf einer einseitig kaschierten Platine in einem Weißblechgehäuse 74 × 148 × 50 aufgebaut, wie Bild 2 zeigt.

Bild 2: Musteraufbau der Oszillatorbaugruppe DJ3RV 008.

Die ICs im Phasenregelkreis sollten im endgültigen Aufbau eingelötet werden.

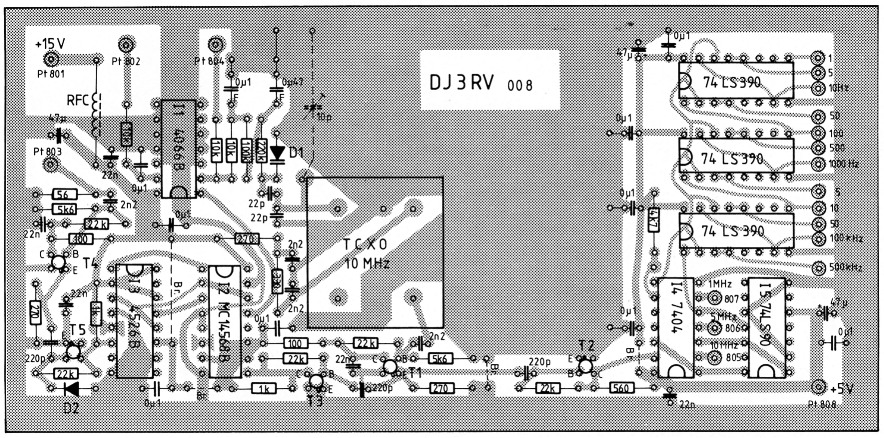

Die Bestückung erfolgt nach dem Plan in Bild 3, und die Spezialbauteile sind in der folgenden Liste aufgeführt.

Bild 3: Bestückungsplan der einseitig kaschierten Platine.

| T1 bis T5 | 2N5179 (RCA) oder ähnlicher UHF-Transistor z. B. BFX89; BFY90 (Siemens, u.a.) |

| I1 | 4066 B (RCA, u. a.) |

| I2 | MC14568 B (Motorola) |

| I3 | MC14526 B (Motorola, u.a.) |

| I4 | 7404 (TI, u.a.) |

| I5 | 4LS90 (TI, u.a.) |

| I6 bis I8 | 74LS390 (TI, u.a.) |

| D1 | BB505G (Siemens, u.a.) |

| D2 | 1N4151 oder ähnlich |

| TCXO | Temperaturkompensierter Quarzoszillator TEKO 10.000 kHz, Valvo, Best. Nr. 4322191 00001 |

| Trimmer | 10 pF Lufttrimmer, Johanson, Typ 5200 |

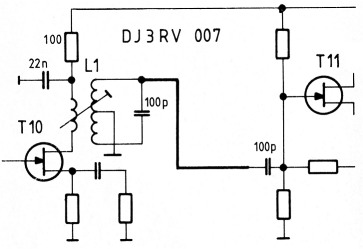

Einige CMOS-Bausteine I2 und I3 können nicht sicher das 6,2-MHz-Signal durch 62 teilen, so daß es notwendig wird, das Referenzsignal mit 3,1 MHz zu benutzen. Dafür müssen auf der Platine DJ3RV 007, wie in Bild 4a gezeigt, die Dioden D4 und D5 und das Filter L2 mit dem Resonanzkreis-Kondensator von 100 pF entfernt, und durch eine Drahtbrücke die gezeigte Verbindung hergestellt werden. Das Ausgangssignal an Pt711 ist dann nicht mehr sinusförmig, sondern schon leicht begrehzt.

Bild 4a: Änderung der Schaltung DJ3RV 007 bei 3,1-MHz-Referenzsignal.

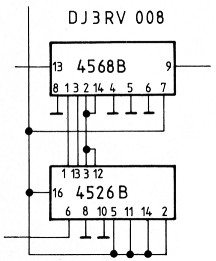

Auf der Platine DJ3RV 008 müssen die Teiler in I2 und I3 dann auf 31 programmiert werden, wie Bild 4b zeigt.

Bild 4b: Änderung der Programmierung auf der Platine DJ 3 RV 008 bei 3,1-MHz-Referenzsignal.

Die beiden Teiler sind in Reihe geschaltet und binär codiert. Die unteren 4 Bit sind an I3 und die oberen 4 Bit an I2 einzustellen.

00011111 ≡ 31

00111110 ≡ 62

Wie die Binärdarstellung der Zahlen zeigt, ändern sich nur zwei Stellen. Das sind Pin 5 an I3 und Pin 6 an I2. Auf der Platine sind diese Stifte noch nicht fest verdrahtet und müssen in jedem Fall durch Lötbrücken programmiert werden!

Für Teilung durch 62: Wie in der Schaltung Bild 1 angegeben: Pin 5/I3 an Masse und Pin 6/I2 an +15 V

Für Teilung durch 31: Pin 5/I 3 an +15 V und Pin 6/I2 an Masse.

Prinzipiell kann die Teilerschaltung auch für andere Referenzfrequenzen bzw. Teilerverhältnisse programmiert werden, wenn die Leitungen auf der Platine entsprechend geändert werden. Wichtig ist dabei, daß die Referenzfrequenz ein ganzzahliges Vielfaches, mindestens das 16-fache von 100 kHz ist, da sich sonst der Teiler in I2 in der vorliegenden Schaltung nicht programmieren läßt.

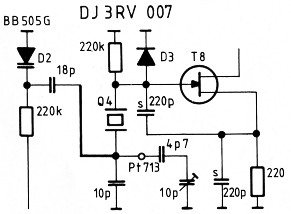

Bei Betrieb der Baugruppen als Zeitbasis für einen Digitalzähler ist es günstiger, die Ringverstärkung im Frequenzregelkreis der Baugruppe DJ3RV 007 zu erhöhen. Die Änderung der Schaltung zeigt Bild 5. Die Kapazitätsdiode D2 wird über den 18-pF-Kondensator an den Hochpunkt des Quarzes Q4 gelegt, und der Serienkondensator auf 10 pF verkleinert. Der Ziehbereich des Quarzes wird dabei größer, jedoch verschlechtern sich die Stabilität und das Rauschverhalten geringfügig. Für diese Änderung sind die Bohrungen und Leitungen auf der Platine bereits vorhanden.

Bild 5: Vergrößerung des Ziehbereichs des Quarzoszillators der Schaltung DJ3RV 007.

3. Inbetriebnahme und Grundabgleich

Nach Anlegen der gut stabilisierten und brummfreien Betriebsspannungen an Pt801 und Pt808, muß an Pt805 ein 10-MHz-TTL-Signal anliegen. Die Werte für die Stromaufnahme sind als Richtwerte zu betrachten. Bei ausgeschaltetem Regelkreis - Pt802 an Masse - muß sich die Frequenz des TCXO mit dem 10-pF-Ziehtrimmer auf exakt 10 MHz ziehen lassen. Nach Einschalten des Regelkreises muß die Frequenz phasenstarr mit der Referenz verkoppelt sein. Die Regelung läßt sich an Pin 2/I1 meßtechnisch überprüfen, wenn die Frequenz durch Berühren von Pin 3 des TCXO kurzzeitig verschoben wird.

Das Einschwingverhalten des Regelkreises wird durch die Zeitkonstante der Siebglieder vor der Diode D1 bestimmt. Im praktischen Betrieb hat sich für den Kondensator ein Wert zwischen 0,22 µF und 2,2 µF bewährt. Der im Schaltbild angegebene Wert von 0,47 µF liefert gute Ergebnisse.

4. Literatur

- Krug, Friedrich: DCF77-Empfänger, UKW-Berichte 24 (1984), Heft 1, S. 42 - 60

DJ3RV, Friedrich Krug.