Taktgeber für Mikrocomputer angekoppelt an DCF77

Für die Rechnerauswertung kohärent übertragener Signale ist ein Zeittakt hoher Stabilität und entsprechender Absolutgenauigkeit erforderlich. Mit dem bereits beschriebenen übersteuerungsfesten und störsicheren DCF77-Empfänger DJ3RV006/007 (1) und der vorliegenden Baugruppe DJ3RV 009 lassen sich die für einen Mikrocomputer notwendigen Takt-Signale - phasenstarr an die Normalfrequenz angebunden - erzeugen. Die Baugruppe liefert für das im letzten Heft der UKW-Berichte (2) angekündigte Mikrocomputersystem den CPU-Takt mit 4 MHz und den Dot-Clock von 16 MHz für die Terminal-Karte.

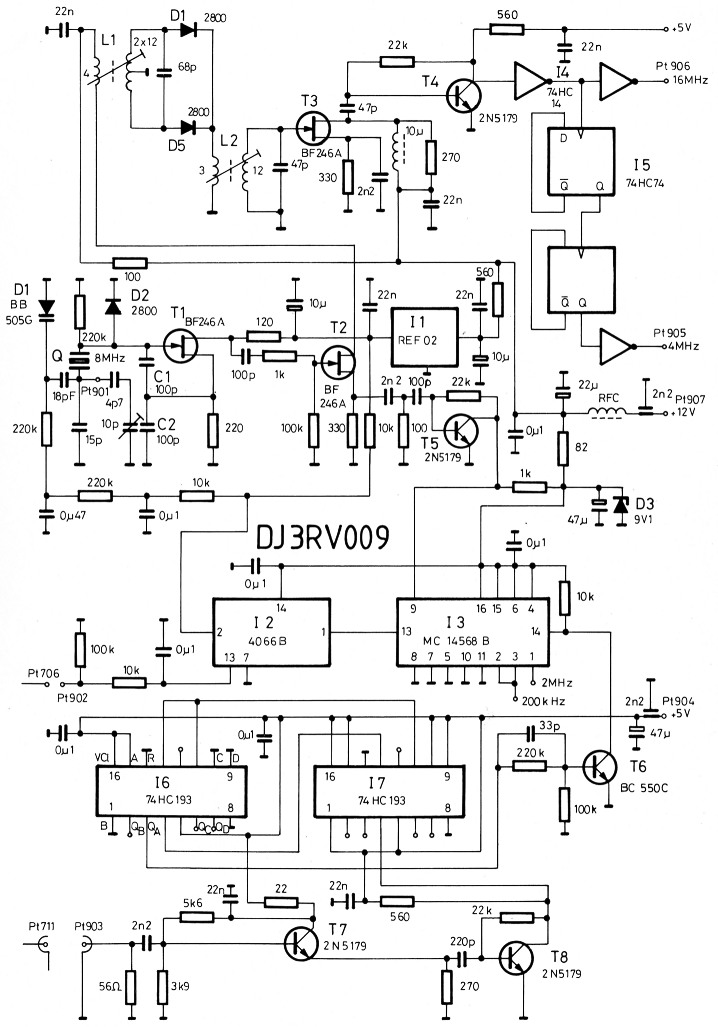

Bild 1: Schaltbild der Taktgeber-Baugruppe.

1. Schaltungsbeschriebung

Die Schaltung der Baugruppe zeigt Bild 1. Der rauscharme Quarzoszillator in Collpits-Schaltung mit dem Sperrschicht-FET T1 ist in dieser Form bereits in der Schaltung D1J3RV 007 verwendet worden. Der Grundwellen Quarz Q schwingt in Parallelresonanz mit 8 MHz und wird über die Serienkapazitäten mit dem Trimmer abgeglichen und mit der Kapazitätsvariationsdiode D1 über die Phasenregelschleife phasenstarr auf die Referenzfrequenz nachgezogen.

Das Oszillatorsignal wird rückwirkungsarm an der Drain von T1 ausgekoppelt, mit T2 verstärkt und auf das Filter L1 und den Pegelwandler T5 verteilt. T5 verstärkt das Signal auf C-MOS-Pegel und steuert den Frequenzteiler in I3 an. Das 8MHz-Signal wird durch 40 geteilt und der Phasenvergleich mit dem von DCF77 abgeleiteten Signal bei 200 kHz durchgeführt. I3 enthält zwei programmierbare Teiler, die in Reihe geschaltet sind. Der erste Teiler ist mit einem Teilungsfaktor 4 : 1 und der zweite mit 10 : 1 fest programmiert. Der Ausgang des ersten Teilers ist an Pin 1 herausgeführt und der des zweiten an Pin 2. Dieses 2-MHz- beziehungsweise 200-kHz-Signal läßt sich zum Abgleich des Quarzoszillators benutzen.

Das Phasendifferenz-Signal am Ausgang des Phasenkomparators wird am Tri-State-Ausgang (Pin 3) abgenommen und regelt über den CMOS-Schalter I2 und die Tiefpasskette mit der Kapazitätsdiode D1 die Phase des Oszillators nach.

Der C-MOS-Schalter I2 öffnet bei Sender-Ausfall oder bei fehlender Baugruppe DJ3RV 007 durch die fehlende Spannung an Pt902, so daß die Diode D1 mit einer Festspannung von + 5 V aus dem Referenzspannungs-Element I1 versorgt wird.

Der Oszillator läuft dann frei und sollte daher so abgeglichen sein, daß er seine Sollfrequenz von 8 MHz bei +5 V an D1 hat.

Das von der Baugruppe DJ3RV 007 an PT903 gelieferte Referenzsignal von 6,2 MHz mit einem Pegel von -6 dBm an 50 Ω wird in T7 verstärkt und mit T8 auf TTL-Pegel gewandelt.

Der fest eingestellte Teilertaktor von 31 : 1 der beiden in Reihe geschalteten Teiler 74 HC193 macht aus dem 6,2-MHz-Signal das zum Phasenvergleich notwendige 200-kHz-Signal, welches mit T6 auf CMOS-Pegel angehoben wird.

Das rückwirkungsarm ausgekoppelte und mit T2 verstärkte 8-MHz-Oszillatorsignal wird mit L1 in ein Gegentaktsignal transformiert und mit den Dioden D4 und D5 frequenzverdoppelt. L1 ist auf die Quarzfrequenz 8 MHz abgestimmt und L2 auf die doppelte Frequenz 16 MHz. Das mit L2 gefilterte 16-MHz-Signal wird mit T3 verstärkt und mit T4 auf TTL-Pegel gewandelt. Der nachfolgende Inverter I4 mit Schmitt-Trigger-Eingang in High-Speed-CMOS-Technologie formt daraus ein Rechtecksignal, welches an das Dual-D-Flipflop I5 und über einen zweiten Inverter auf den Rechner-BUS gegeben wird. I5 ist als Teiler 4 : 1 geschaltet. Das auf 4 MHz geteilte Signal wird über einen weiteren als Treiber verwendeten Inverter ebenfalls auf den Rechner-BUS gekoppelt.

Die für den Betrieb der Schaltung benötigten Spannungen von +5 V und +12 V liefert ebenfalls der Rechner-BUS. Aus der +12-V-Spannung wird mit der 9,1-V-Zenerdiode die Betriebsspannung für die CMOS-Bausteine I2 und I3 und die zugehörigen Treiber erzeugt. Ebenfalls aus der +12-V-Spannung stabilisiert I2 eine hochstabile, rauscharme Betriebsspannung von +5 V für den Oszillator. Die schon vom BUS vorhandene +5-V-Versorgungsspannung ist für den Oszillator ungeeignet, da die Stabilität nicht ausreicht und durch die Rechner-Aktivität auch relativ stark mit Störungen "verseucht" ist.

2. Aufbauhinweise

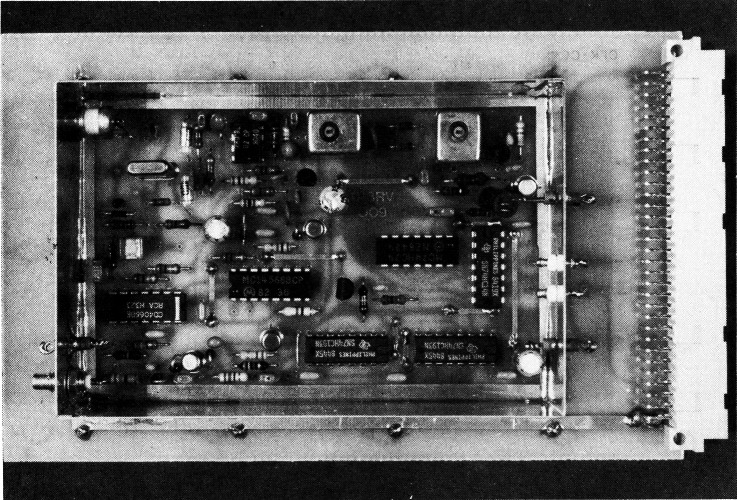

Wie aus dem Musteraufbau in Bild 2 ersichtlich, ist die Schaltung auf einer beidseitig beschichteten Platine in Europaformat 100 mm x 160 mm aufgebaut und mit einem aufgelöteten Weißblechgehäuse abgeschirmt, um die Gefahr einer Einstreuung gering zu halten.

Bild 2: Auf der Unterseite ist der zweite Deckel des Weißblechgehäuses unmittelbar auf die Leiterplatte gelötet.

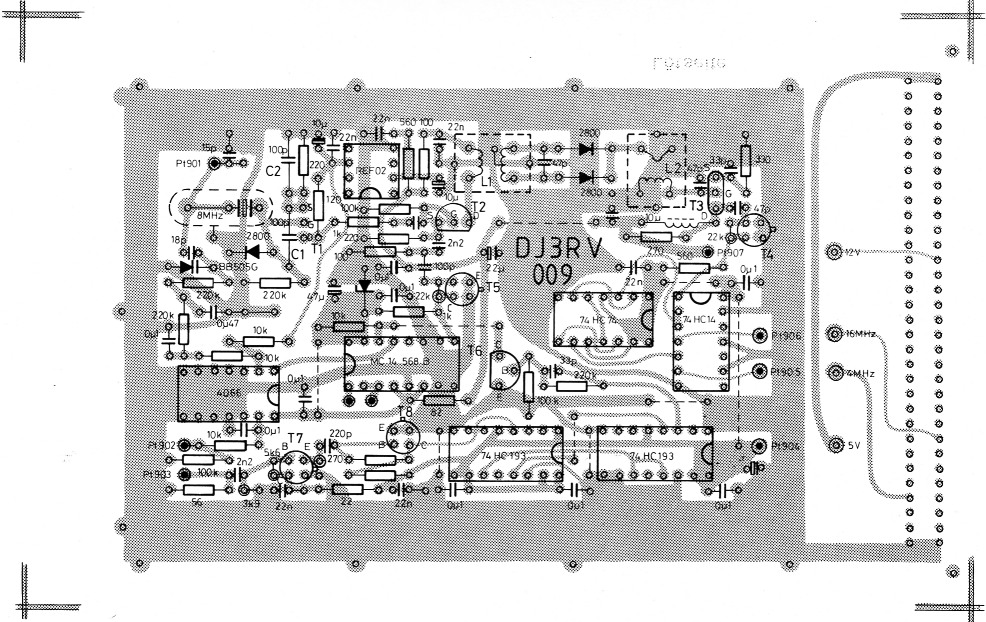

Der Aufbau nach Bild 3 ist problemlos und stellt in etwa die gleichen Anforderungen wie die dazugehörenden und schon in (1) beschriebenen Baugruppen DJ3RV 006 und 007. Die Daten der Bauteile sind der folgenden Stückliste zu entnehmen.

Bild 3: Bestückungsplan der Platine DJ3RV009; es sind 9 Brücken im Bestückungsbereich und 11 Masse-Verbindungen am Gehäuse durchzukontaktieren.

2.1. Stückliste

| T1,T2,T3 | BF246A (Tl ,u.a.) |

| T4,T5,T7,T8 | 2N5179 (RCA) oder ähnlicher UHF-Transistor z. B. BFX89; BFY90 (Siemens, u. a.) |

| T6 | BC550C (Siemens, u. a.) |

| I1 | REF02 (PMI, Boums) |

| I2 | 4066B (RCA, u. a.) |

| I3 | MC14568B (Motorola) |

| I4 | 74HC14 (TI, u. a.) |

| I5 | 74HC74 (TI, u. a.) |

| I6,I7 | 74HC193 (TI, u. a.) |

| D1 | BB505G (Siemens, u. a.) |

| D2,D4,D5 | 2800 (HP, u. a.) |

| D3 | Zenerdiode 9V2 |

| L1 | Filterbausatz Vogt D 41-2165, Farbe orange 2 × 12 Wdg., 0,2 CuL, 7 µH 4 Wdg., 0,2 CuL |

| L2 | Filterbausatz Vogt D 41-2165 Farbe orange 12 Wdg., 0,2 CuL, 1.7 µH 3 Wdg., 0,2 CuL |

| Q | 8,000 MHz, parallel 20 pF |

| Trimmer | 10-pF-Lufttrimmer Johanson Typ 5200 |

| C1,C2 | 100 pF, Styroflex |

Alle im Schaltbild nicht besonders gekennzeichneten Bauelemente können als Standardbauteile mit den angegebenen Werten eingesetzt werden.

Widerstände: Metallschicht Typ 0207

Kondensatoren: keramische Kondensatoren mit RM = 2,5 mm, teilweise RM=5mm

3. Abgleich-Hinweis

Der Abgleich des Quarzoszillators erfolgt mit offenem Pt902 auf exakt 2000000 Hz an Pin 1 von I3. Die Spulen L1 und L2 werden danach auf maximales Signal an der Drain von T3 abgeglichen. Damit ist die Baugruppe betriebsbereit und kann auf den Rechner-BUS aufgesetzt werden. Dabei ist zu beachten, daß die auf der CPU-Platine und der Terminal-Platine vorhandenen Taktgeneratoren herausgezogen beziehungsweise abgeklemmt werden müssen.

4. Literatur

- Krug, Friedrich: DCF77-Empfänger, UKW-Berichte 24 (1984), Heft 1, S. 42 - 60

- Jirmann, J.; Krug, F.: Ein Mikrocomputer-System für Amateurfunk-Anwendungen, UKW-Berichte 25 (1985), Heft 3, S. 184 - 186

DJ3RV, Friedrich Krug.