Upconverter van 0 tot 30 MHz naar 144 MHz 1

Beschrijving van de werking en de bouw van een upconverter waarmee met een SSB 2 meter-set, bijvoorbeeld een FT290, de gehele frequentieband tussen 10 kHz en 30 MHz beluisterd kan worden.Algemene werking

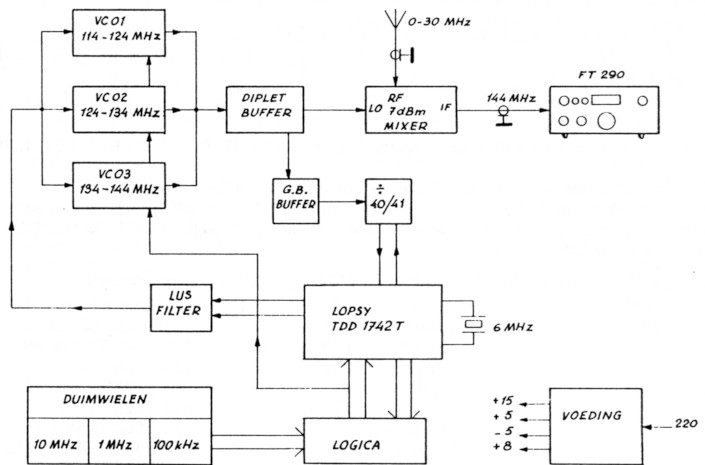

Blokschema.

Een binnenkomend signaal wordt in een dioderingmixer omhoog gemengd naar 144 MHz door een met een PLL opgewekt signaal.

De dioderingmixer kent drie aansluitingen, namelijk:

RF - ingang voor het ingangssignaal 0-30 MHz

LO - Local oscillator, het PLL signaal

IF - uitgang met som- en verschil-frequentie van beide andere signalen, het 144 MHz signaal

Er zijn twee mogelijkheden voor de op te wekken LO-frequenties:

- LO freq. = IF freq. + RF freq., of

- LO freq. = IF freq. - RF freq.

- Bij toenemende ingangsfrequentie, de RF frequentie, neemt de uitgangsfrequentie, de IF frequentie, af. Hierdoor loopt de afstemschaal op de 2 meter ontvanger tegengesteld! Dit is erg lastig voor het aflezen van de ontvangstfrequentie.

- Bij deze oplossing loopt de afstemschaal normaal op.

Gekozen is daarom voor b). De op te wekken LO frequentie is dus 144 - (0 t/m 30) = 144 t/m 114 MHz. De mixer heeft voor de LO ingang een signaalniveau van circa + 7 dBm nodig.

Het LO signaal wordt opgewekt met drie oscillatoren (VCO's), die elk een gebied van 10 MHz bestrijken. Door telkens maar een van de drie VCO's in te schakelen kunnen de drie uitgangssignalen bij de ingang van een buffer aan elkaar geknoopt worden. Deze buffer versterkt het VCO-signaal tot het benodigde niveau.

Een extra buffer zorgt voor aansturing van een voordeler, die de oscillatorfrequentie door 40 deelt naar een voor het PLL IC, de TDD1742T, te verwerken frequentie.

Het laatstgenoemde IC bevat een groot aantal schakelingen die voor de opbouw van een PLL nodig zijn. Dit zijn: een oscillator voor het referentiesignaal, een instelbare referentiedeler, een instelbare hoofddeler voor het VCO signaal, twee fasedetektoren en logika voor de programmering en de besturing van dit alles.

De programmering werkt met behulp van 3 adres- en 4 data-lijnen.

Het lusfilter, geplaatst tussen de fasedetektoren en de VCO's filtert de referentiefrequentie uit en is bepalend voor de snelheid waarmee de lus vergrendeld raakt.

De stuurlogika voert op de kode van de duimwielen een bewerking uit zo dat de juiste signalen ontstaan voor het PLL IC om de ingestelde frequentie te kunnen ontvangen.

De voeding zorgt voor het opwekken van de benodigde voedingsspanningen van +5, -5, +8 en +15 Volt.

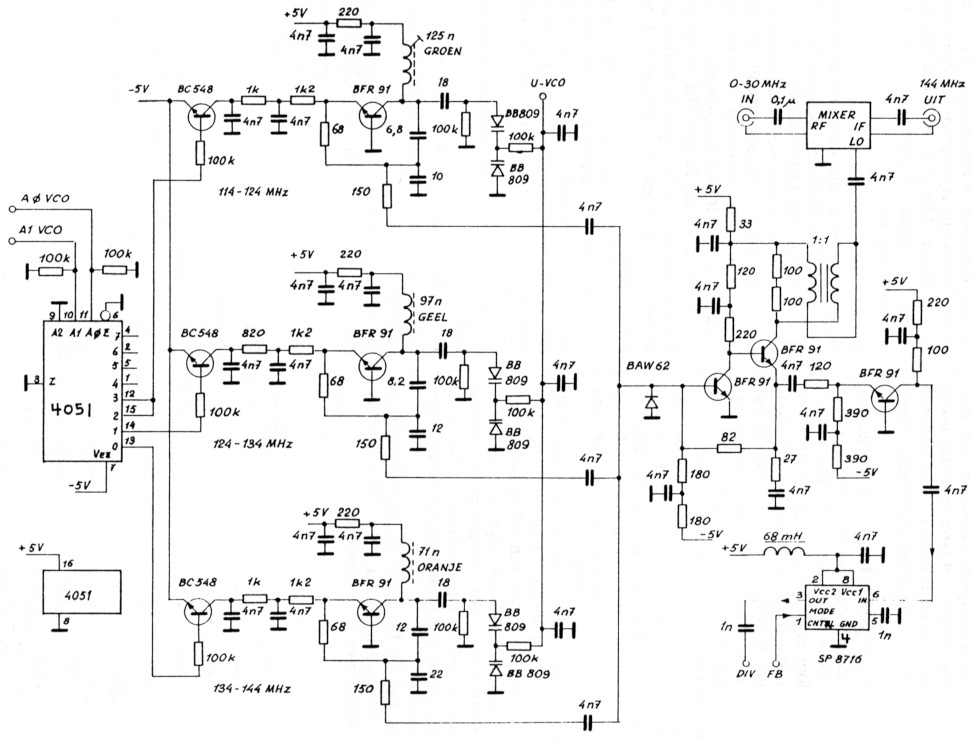

VCO's

De VCO's (fig. 1) wekken de LO frequentie op, welke loopt van 114 MHz tot 144 MHz. Dit is een te groot gebied om met een enkel VCO op te wekken zonder dat dit ten koste gaat aan de goede werking of eenvoud. Om deze reden is gekozen voor opsplitsing in drie bereiken van elk 10 MHz met aan boven- en onderzijde 2 MHz extra i.v.m. temperatuurinvloed.

Fig. 1.

De gebruikte schakeling is een Collpits oscillator met een transistor in geaarde basisschakeling. De basis is direkt en zo kort mogelijk met aarde verbonden om de kans op parasitaire oscillaties zo klein mogelijk te maken. Dit betekent wel dat er voor de instelstroom een -5V voedingsspanning nodig is.

Het oscillatorsignaal wordt van de kring in de collector d.m.v. kapacitieve deling op de emitteringang teruggekoppeld. Op ditzelfde punt wordt het signaal naar de buffer toe afgenomen. Twee varicap's zorgen voor de afstemming van de VCO frequentie.

Het in- en uitschakelen van de VCO's vindt plaats door het schakelen van de emitterstroom van de oscillator. De instelling van het 10 MHz duimwiel bepaalt via de multiplexer welke van de drie oscillatoren ingeschakeld is.

Omdat telkens maar een van de VCO's ingeschakeld is, kunnen de uitgangen en de regelspanningsingangen van de drie VCO's met elkaar verbonden zijn.

De spoelen in de VCO's zijn kant en klare spoelen, type S18 van Philips, welke van een ferriet of aluminium kern kunnen worden voorzien voor het verhogen resp. verminderen van de zelfinduktie.

Bij het ontwerp is getracht er voor te zorgen dat geen afregeling nodig is, ofwel spoelen zonder kern. Bij het VCO voor het laagste bereik is toch een ferrietkern nodig om het juiste afstembereik te krijgen.

Buffers

De buffers (fig. 1) moeten het VCO-signaal versterken tot een signaal dat voldoende is voor de mixer en de 40/41 deler.

Voor de mixer is een diplet gebruikt. Dit is een met twee transistoren opgebouwde stroomtegengekoppelde versterker met lage ingangsimpedantie. Dit type versterker is erg breedbandig en dient zorgvuldig opgebouwd te worden om parasitaire oscillaties te voorkomen.

Om de mixer goed te laten werken is het belangrijk dat de sturende versterker een korrekte 50 Ohm impedantie heeft. Dit is te bereiken door in de collector van de diplet een 50 Ohm weerstand op te nemen. Hierdoor gaat echter de helft van het op te wekken signaal in de weerstand zitten. Er is daarom gebruik gemaakt van een 'langelijntrafo' die een transformatie van 1:2 veroorzaakt.

Hierdoor kan een 200 Ohm collectorweerstand gebruikt worden en kan de versterking van de diplet 6 dB kleiner zijn. Bovendien is in dit geval de instelstroom aanzienlijk kleiner, wat in het 50 Ohm geval problemen zou geven met de dissipatie.

De langelijntrafo is het enige 'moeilijke', maar onvermijdelijke onderdeel in deze schakeling. De trafo kan zelf gemaakt worden door op een kleine ringkern (diameter ca 5 mm) twee getwiste posyndraadjes 7 maal door te steken. De aansluiting is het beste door een tekening aan te geven (zelfde als een 'balun').

Ook kan een kant en klare langelijntrafo gebruikt worden van het merk TMO. Hiermee is echter geen proef genomen.

De buffer voor de 40/41 deler is opgebouwd met een transistor in een geaarde basisschakeling. Deze krijgt zijn signaal van de emitter van de diplet. Met deze buffer wordt het oscillator signaal versterkt tot een 500 mVtt signaal.

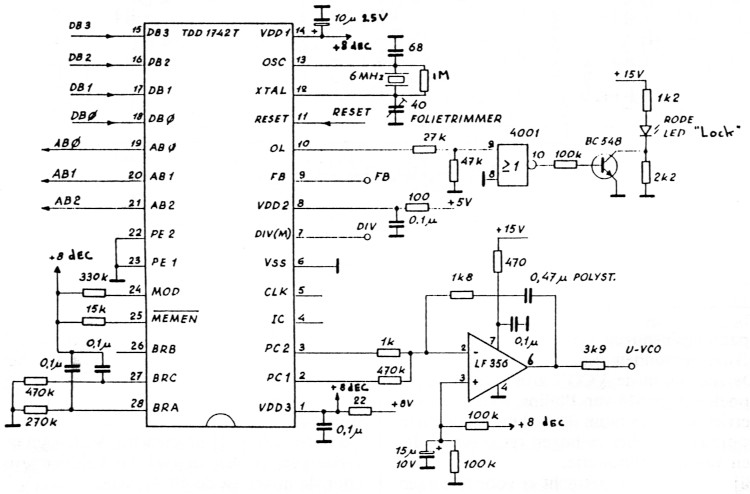

Het PLL IC

Het onderdeel waar alles om draait in dit ontwerp is het Low Power Synthesyser LOPSY IC van Philips, de TDD1742T (fig. 2). Zoals de naam al doet vermoeden gaat het om een IC met laag stroomverbruik. De behuizing is een SMD uitvoering waardoor het solderen van het IC wat priegelwerk is. Zelf heb ik het IC op een 28 pins DIL voetje gelijmd en dunne draadjes naar de pennen gesoldeerd waarmee een soort 28-pens DIL IC is verkregen.

Fig. 2.

De referentiefrequentie van 12,5 kHz wordt na deling door 480 met een 6 MHz kristal verkregen. Een trimmer zorgt voor de afregeling. Het deeltal wordt verkregen door de instelling van de referentiedeler op: 4 (vast), 12, 5 en 2.

Het deeltal van de VCO frequentie wordt bepaald door:

D = (128 × n2 × n1) × 40 + n0

waarbij n0, n1 en n2 7-bits binaire getallen zijn met n2 ≥ 1.

De bits worden met 4 tegelijk ingelezen op DB0 t/m DB3, waarbij het bijbehorende adres 000 t/m 111 door een interne teller wordt gegenereerd op AB0 t/m AB3. Deze teller, en daarmee de inleescyclus, wordt door een resetsignaal op pen 11 gestart. Het deelal van de 40/41 deter, 40 of 41, wordt vanuit dit LOPSY IC gestuurd met het signaal FB. Dit zorgt ervoor dat de frequentie van de PLL met stappen van 12.5 kHz instelbaar is i.p.v. 40 × 12.5 = 500 kHz. Het door deze prescaler verkregen signaal wordt op pen 7 aangesloten.

De TDD I742T kan een PROM aansturen die de duimwielkode konverteert in de benodigde bits. Dit is niet gedaan, omdat de opbouw van de benodigde logika eenvoudiger leek dan het bouwen van een EPROM programmer (in CQ-DL stond zo'n schema met EPROM).

Er zijn twee fasedetektoren aanwezig PC1 en PC2. PC2 is een digitale fase-frequentie detektor die voor het snel invangen van de lus dient. PC1 is een bijzondere analoge fasedetektor met een grote versterking die voor de goede eigenschappen van deze PLL zorgt. Dit type fasedetektor komt nog maar weinig voor: o.a. in de HEF4750 (deze ruist echter!) en NJ8820 (zie recent artikel in UKW Berichte).

De weerstand verbonden met pen 28 zorgt voor de instelstroom van fasedetektor PC1. De weerstand aan pen 27 is voor de instelstroom van interne analoge circuits.

De Out of Lock detektor geeft zijn signaal op pen 10 af, waarmee een led gestuurd wordt, die bij het niet werken van de lus minder gnat branden. Deze led is n.l. ook voor aan/uit indikatie. De voedingsspanningen voor dit IC zijn 5V op pen 8 voor de Ili compatible' circuits en 7 tot 10V voor de overige digitale en analoge schakelingen op resp. pen 14 en pen 1. Gekozen is hier voor 8V.

De programmering van de TDD1742T is volgens de tabel:

| AB2 | AB1 | AB0 | DB3 | DB2 | DB1 | DB0 | Opmerkingen |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | testmode uit |

| 0 | 0 | 1 | n03 | n02 | n01 | n00 | LSB's van n0 |

| 0 | 1 | 0 | R00 | n06 | n05 | n04 | refer., MSB's van n0 |

| 0 | 1 | 1 | n13 | n12 | n11 | n10 | LSB's van n1 |

| 1 | 0 | 0 | R01 | n16 | n15 | n14 | refer., MSB's van n1 |

| 1 | 0 | 1 | n23 | n22 | n21 | n20 | LSB's van n2 |

| 1 | 1 | 0 | M | n26 | n25 | n24 | modul., MSB's van n2 |

| 1 | 1 | 1 | R21 | R20 | R11 | R10 | referentie delerbits |

De programmering van de referentiedelers is volgens :

| R01 | R00 | Deeltal | R11 | R10 | Deeltal | R21 | R20 | Deeltal |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 12 | 0 | 0 | 9 | 0 | 0 | 1 |

| 0 | 1 | 13 | 0 | 1 | 5 | 0 | 1 | 2 |

| 1 | 0 | 14 | 1 | 0 | 6 | 1 | 0 | 4 |

| 1 | 1 | 15 | 1 | 1 | 7 | 1 | 1 | 8 |

Om de referentiedeler op 480 in to stellen is de code voor R01, R00, R11, R10, R21, R20 = 00 01 01.

Het M bit van de tabel zet de modulator aan of uit en moet hier dus 0 zijn.

Voor het instellen van de hoofddeler is van de bits voor n2 alleen n20 en n21 nodig, zodat de andere bits van n2 vast op 0 zijn ingesteld. Door de inverters welke voor DB0 t/m DB3 geplaatst zijn wordt de benodigde kode:

| AB2 | AB1 | AB0 | DB3' | DB2' | DB1' | DB0' | Opmerkingen |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 1 | 1 | testmode uit |

| 0 | 0 | 1 | n03' | n02' | n01' | n00' | LSB's van nO |

| 0 | 1 | 0 | 1 | n06' | n05' | n04' | ROO', MSB's van nO |

| 0 | 1 | 1 | n13' | n12' | n11' | n10' | LSB's van n1 |

| 1 | 0 | 0 | 1 | n16' | n15' | n14' | R01', MSB's van n1 |

| 1 | 0 | 1 | 1 | 1 | n21' | n20' | n23', n22', LSB's n2 |

| 1 | 1 | 0 | 1 | 1 | 1 | 1 | M', MSB's van n2 |

| 1 | 1 | 1 | 1 | 0 | 1 | 0 | R21', R20', R11', R10' |

Lusfilter

Het lusfilter is bepalend voor het regelgedrag van de PLL.

De kapaciteit in het filter moet lekarm zijn, zoals bijvoorbeeld een polystyreen type. De weerstand van 3k9 vormt met de drie 4n7 condensatoren bij de VCO's een extra laagdoorlaatfilter. Deze condensatoren mogen dus geen andere waarde hebben. De overige 4n7 C's mogen ook een waarde van 3n3 tot 10n hebben.

In deel 2 worden de multiplexer, duimwiel decoder, reset, voeding en opbouw beschreven.... natuurlijk met de bijbehorende schema's.

PE1AXH, Norbert van den Bos.

Deel 1 - deel 2.