PLL-Oszillatoren mit Verzögerungsleitung 5

Digitale Frequenzeinstellung

Die im 1. Teil dieser Aufsatzreihe(1) zitierte "analoge Betriebsweise" (Drehknopf zur Frequenzeinstellung) mag für konventionellen Funkbetrieb die optimale (weil gewohnte) Lösung sein. Um neuartige Übertragungstechniken realisieren zu können (unter Einsatz des Stationscomputers), ist es mitunter jedoch wünschenswert, bestimmte Bedienfunktionen eines Empfängers oder Transceivers (Betriebsart, Bandbreite, Frequenz u. s. w.) mit "Rechnerzugriff" auszustatten. Während kommerziell gefertigte Amateurfunkgeräte zunehmend mit mehr oder weniger genormten "Schnittstellen" ausgerüstet angeboten werden, fand dieser Aspekt bei Eigenbaugeräten bisher kaum Beachtung.

Wie im Laufe dieser Artikelserie bereits mehrfach erwähnt, ist der beschriebene PLL-VLOszillator (2), (3) von Natur aus gut für ferngesteuerten Betrieb geeignet. Der hier vorliegende Bericht beschreibt eine Baugruppe, die anstelle des (teuren) Sinus-CosinusPotentiometers die Steuerung des Oszillatorteils DK1OF 046 übernehmen kann und zwar auf zwei verschiedene Arten:

- Handsteuerung Aufwärts / Abwärts mit je vier Abstimmgeschwindigkeiten

- Vorgabe eines Frequenz-Sollwertes, Vergleich mit Zähler-Istwert, kontinuierliche Nachstimmung

7.1. Ein wenig Theorie

Im Abschnitt 1 des 1. Teils dieser Arbeit wurde erklärt, daß eine volle "Knopfumdrehung" am Phasenschieber einem Abstimm-Intervall von 1/64 µs - 15.625 kHz entspricht (siehe hierzu auch Bild 8 in (1). Will man das dort erwähnte Sinus-Cosinus-Potentiometer durch Digital/ Analog-Wandler (DACs) ersetzen, so stellt sich natürlich sofort die Frage nach der notwendigen Auflösung, d. h. wie groß der kleinste vollziehbare Frequenzschritt sein darf. Für SSB und RTTY wäre eine Schrittweite von 10Hz wünschenswert, so daß eine "Umdrehung" in ca. 1500 Stufen zu zerlegen wäre. Selbstverständlich gibt es entsprechend "feinstufige" DACs, diese zählen jedoch nicht zu den Standardbauteilen und sind deshalb teuer.

Verwendet man 8-Bit-DACs (VP-Standard), so läßt sich das Abstimm-Intervall von 15625 Hz in 512 Stufen unterteilen, was einer Schrittweite von 30,5 Hz entspricht. Dieser Wert erscheint ausreichend; man hat überdies ja noch die Möglichkeit einer Analog-Interpolation (Potentiometer P2 in Bild 19 von (2), die man mit einem weiteren DAC auch noch digital ansteuerbar ausführen kann.

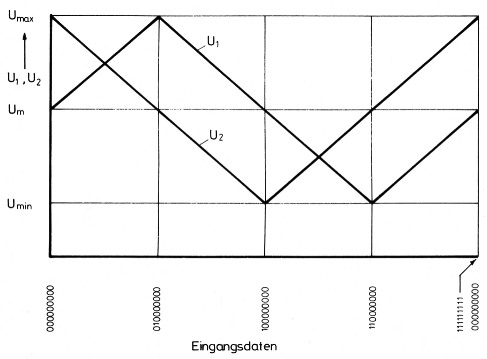

Dem aufmerksamen Leser wird sicher aufgefallen sein, daß behauptet wurde, man könne mit 8bit-DACs (28 = 256 Werte) 512 Abstimmstufen realisieren. Betrachtet man Bild 35, so wird klar, daß der gesamte Ausgangs-Spannungsbereich jedes DACs zweimal durchfahren wird, und zwar einmal mit steigenden und einmal mit fallenden Spannungswerten. So ergeben sich in der Tat 2 × 256 = 512 Abstimm-Inkremente.

Bild 35: Benötigte Steuerspannungen U1 und U2 in Abhängigkeit von den Eingangsdaten.

Der in Bild 8 dargestellte sinus- bzw. cosinusförmige Verlauf der Steuerspannungen für den Phasenschieber muß nicht unbedingt eingehalten werden, man kann stattdessen die "natürlichen" linearen Rampen der DACs verwenden. Zwar ist dann die Schrittweite entlang der Abstimmkurve nicht mehr konstant; die Abweichung beträgt jedoch nur einige Prozent, was in der Praxis ohne Bedeutung ist. Gewiß könnte man Netzwerke aus Widerständen und Dioden zur Approximation der Sinuskurve vorsehen (was auch erprobt wurde), doch scheint mir dieser Aufwand nicht gerechtfertigt. Außerdem besteht die Gefahr, daß durch die Temperaturabhängigkeit der Diodenkennlinien unnötige Frequenz-driften des Oszillators entstehen.

7.2. Schaltung der Steuerbaugruppe

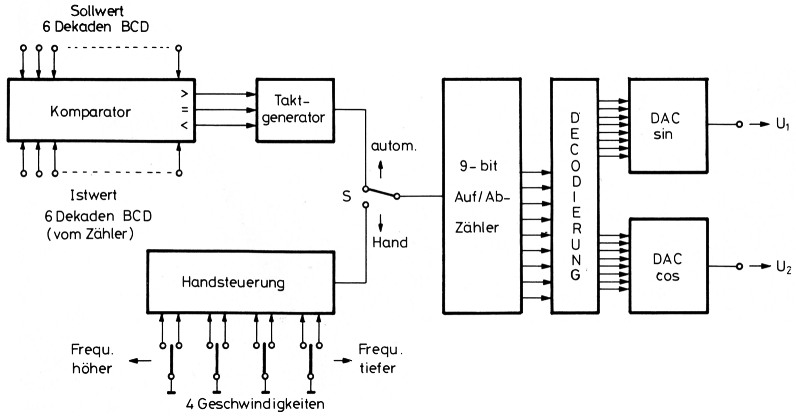

Bild 36 zeigt zunächst das Blockschaltbild. Frequenz-Sollwert (= Eingabe) und lstwert (= Zählerstand) werden einem Digital-Komparator (= Vergleicher) zugeführt; als Datenformat wurde der BCD-Code gewählt, um Kompatibilität mit anzeigenden Frequenzzählern zu erzielen.

Bild 36: Blockschaltbild der digitalen Frequenzeinstellung.

Natürlich muß auch der Sollwert im BCD-Code eingegeben werden, z. B. über Ziffernschalter oder eine Rechner-Parallelausgabe mit 24 Bit (6 Dekaden mit je 4 BCD-Bits). Die Ausgänge des Komparators (zu hoch, richtig, zu tief) sind mit einem Taktgenerator verbunden, der über den Umschalter S einen 9-Bit-Binärzähler aufwärts oder abwärts zählen läßt, je nachdem, ob der lstwert kleiner oder größer ist als der Sollwert. Die Ausgänge des Binärzählers werden durch eine Gatterschaltung so decodiert, daß die nachfolgenden D/A-Wandler die Spannungen U1 und U2 entsprechend Bild 35 abgeben.

Steht der Umschalter S in Stellung "Hand", so kann die Baugruppe über Drucktaster manuell bedient werden. Dabei sind Frequenzkorrekturen nach oben und unten mit vier abgestuften Geschwindigkeiten möglich.

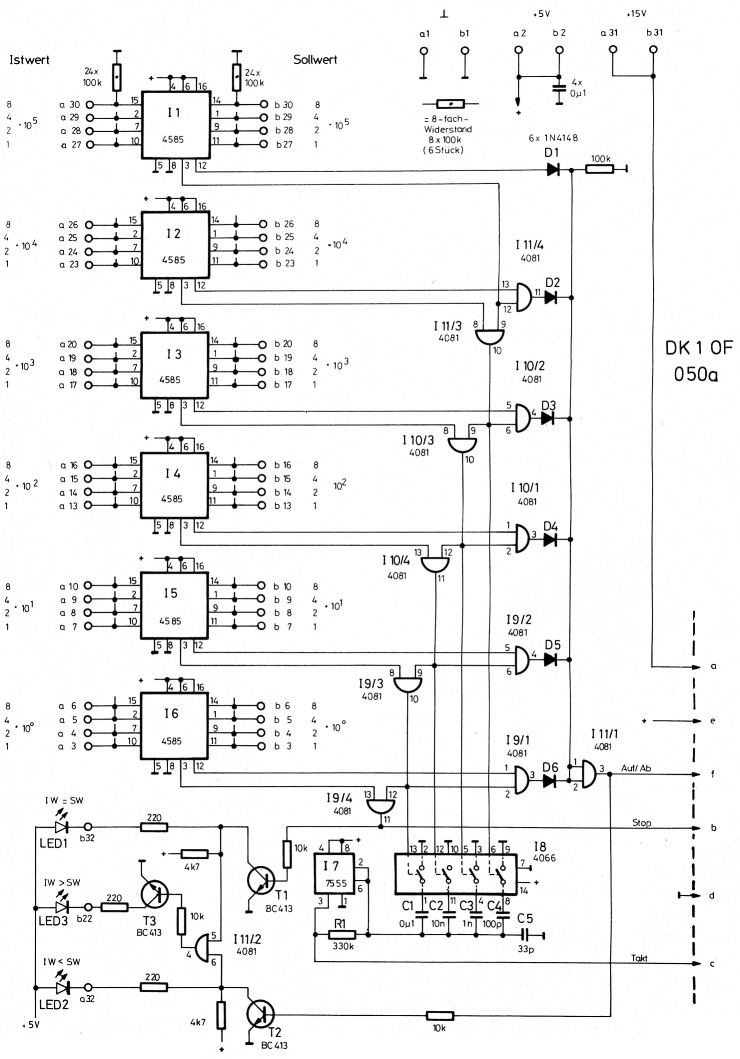

Der besseren Übersicht wegen wurde das ausführliche Schaltbild auf drei Zeichnungen aufgeteilt. Bild 37 zeigt den Digital-Komparator mit seinen 2 × 24 BCD-Eingängen für Ist- und Sollwert (I1 bis I6) sowie den Taktgenerator (I7). Der Schaltkreis I8 hat die Aufgabe, die von I7 erzeugte Taktfrequenz je nach dem Grad der Übereinstimmung an den Digitaleingängen umzuschalten. Dies bewirkt, daß bei großen Abweichungen zwischen Soll- und Istwert schnell nachgeregelt wird. Die "Feineinstellung" dagegen (Abweichungen nur in den niederwertigen Dekaden) muß so langsam geschehen, daß der Zähler genug Zeit hat, der sich während des Korrekturvorgangs noch ändernden Frequenz zu folgen. Sonst würde der Regelkreis instabil, das heißt um den richtigen Wert pendeln.

Bild 37: Komparator und Takt-Generator.

Zeigen alle Dekaden Übereinstimmung, dann geht der Ausgang des Gatters I9/4 auf H-Pegel, über Anschluß b wird der Binärzähler gestoppt und T1 schaltet die Leuchtdiode LED1 ein, welche den eingeregelten Zustand signalisiert. Bei Nichtübereinstimmung brennt entweder LED2 oder LED3, je nachdem, ob der lstwert kleiner oder größer ist als der Sollwert.

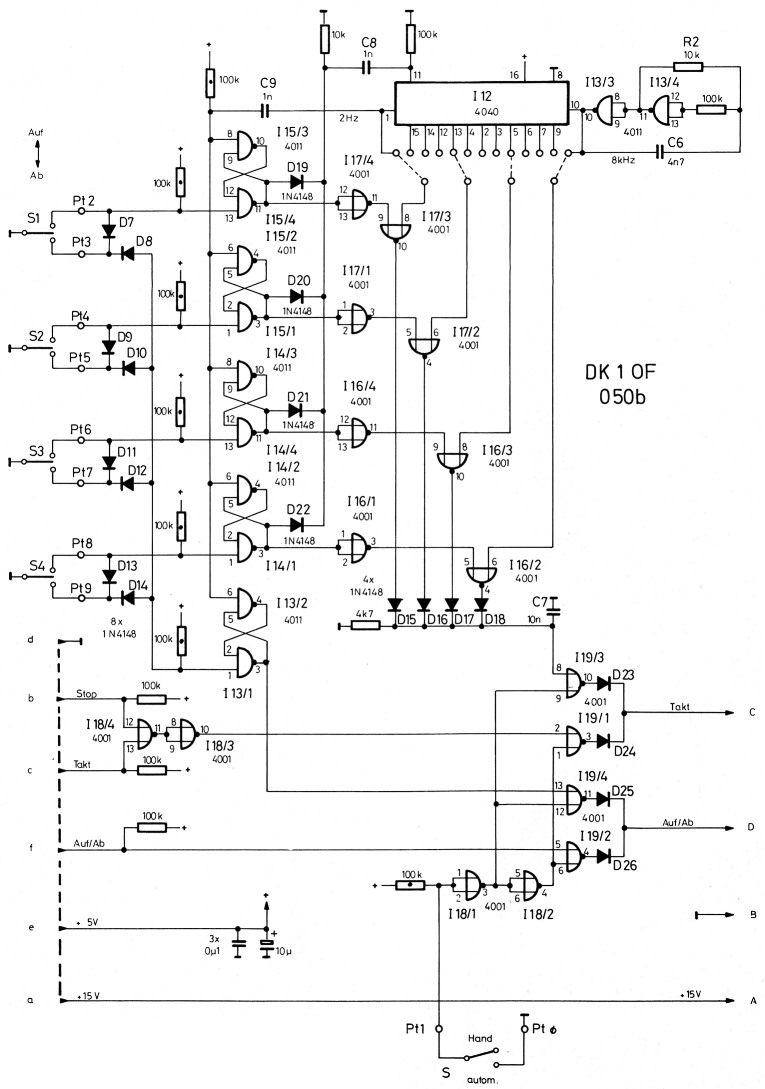

Wir kommen nun zu Bild 38. Rechts oben ist ein astabiler Multivibrator mit den Gattern I13/3 und I13/4 zu sehen. Er schwingt mit etwa 8 kHz, was durch R2 und C6 festgelegt wird. Diese Frequenz wird nun in I12 durch 212 (= 4096) geteilt, so daß an dessen Pin 1 ein Rechtecksignal mit 2 Hz ansteht. Alle Zwischenwerte (4, 8, 16, 32 Hz u. s. w.) stehen an den "Anzapfungen" von I12 zur Verfügung. Links daneben erkennt man fünf RS - Flipflops, die aus den Gattern mit I15, I14 und der restlichen Hälfte von I13 aufgebaut sind. Wird nun beispielsweise die Taste S1 kurz nach oben getippt, so kippt das oberste RS - FF in seine Arbeitslage; über D19 und C8 erhält der Teiler I12 einen kurzen Rücksetzimpuls, er beginnt also nun von Null ausgehend hochzuzählen. Nach 4096 Taktimpulsen (also eine halbe Sekunde später) ist ein voller Zyklus abgezählt und an Pin1 von I12 erscheint eine H → L-Flanke. Diese setzt über C9 das RS-FF wieder zurück, wenn bis zu diesem Zeitpunkt S1 losgelassen wurde. Über I17/3, D15, I19/3, D23 und Anschluß C erhält der 9-Bit-Binärzähler einen einzelnen Taktimpuls, der ihn um eine Stelle weiterschaltet und damit die erzeugte Oszillatorfrequenz um ca. 30 Hz erhöht. Das gleiche geschieht sinngemäß, wenn eine der anderen Tasten (S2, S3 oder S4) betätigt wird. Jedoch mit dem Unterschied, daß dann nicht ein einzelner Impuls, sondern ein ganzes Paket (Frequenz je nach verwendeter Anzapfung von I12) von Zählimpulsen abgegeben wird. Benutzt man die in Bild 38 gestrichelt angedeuteten Brücken, so ergeben sich folgende Werte:

| Taste | Anzahl der Zählimpulse | Frequenzänderung |

|---|---|---|

| S1 | 1 | 30,5 Hz |

| S2 | 16 | 488 Hz |

| S3 | 256 | 7,81 kHz |

| S4 | 4096 | 125 kHz |

Bild 38: Handsteuerung.

Wird eine Taste dauernd gedrückt, so bleibt das betreffende FF in seiner Arbeitslage (der Reset-Impuls wird ignoriert). In diesem Fall wird an C ein stationäres Rechtecksignal abgegeben und die erzeugte Frequenz läuft kontinuierlich hoch.

Bewegt man eine der Tasten nach unten, so wird außer dem jeweils angesprochenen FF zusätzlich auch das unterste FF (mit I13/1 und I13/2) gesetzt. Über I19/4, D25 und Anschluß D erhält der 9-Bit-Zähler dann den Befehl, die Zählrichtung umzukehren, wodurch die erzeugte Oszillatorfrequenz erniedrigt wird. C7 hat die Aufgabe, die Zählimpulse etwas zu verzögern, damit genügend Zeit für die Richtungsumkehr bleibt.

Die eingangs erwähnte Umschaltung Hand / Automatik wird von den Gattern I19/1 bis /4 sowie I18/1 und /2 vorgenommen. Die Versorgungsspannung für alle bisher besprochenen Schaltungsteile beträgt +5 V.

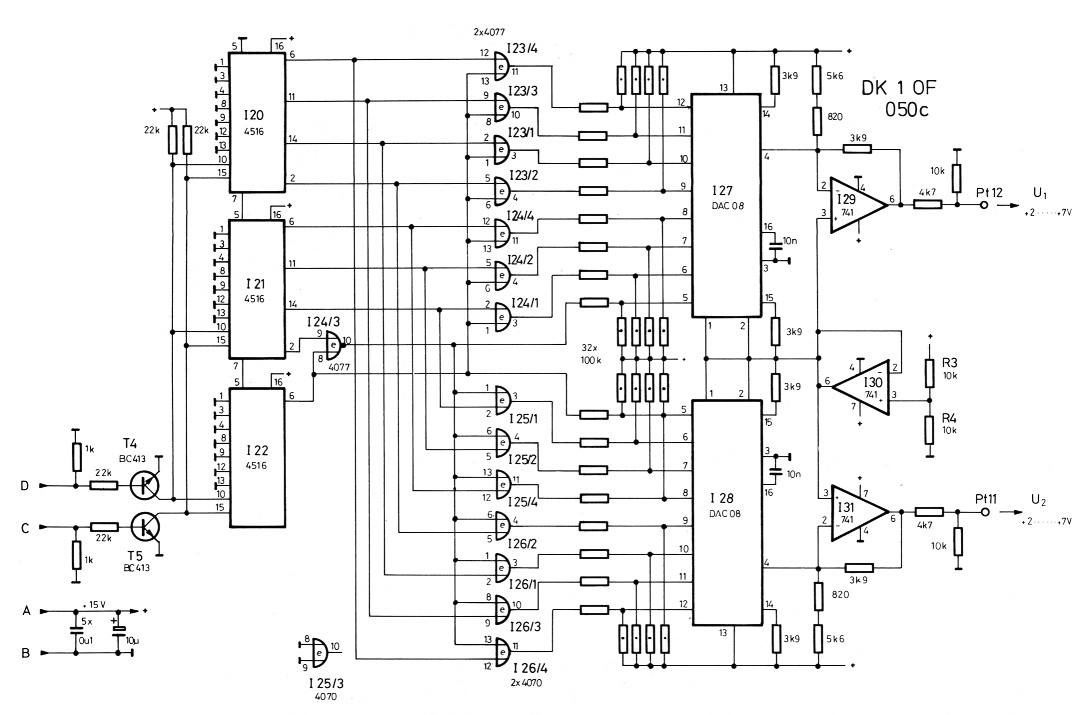

Die restlichen Stufen der Schaltung sind in Bild 39 dargestellt. I20, I21 und I22 bilden den 9-Bit-Binärzähler; da dieser Schaltungsteil mit +15 V versorgt wird, sind T4 und T5 als Pegelwandler für Takt- und Umschaltsignal vorgesehen. Die Decodierung des Binärwertes (um die DAC-Daten zu erhalten, vgl. Bild 35) übernehmen die exclusiv-or- bzw. exclusiv-nor-Gatter I23 bis I26.

Bild 39: Binärzähler, Decodierung und D/A-Wandler.

Die verwendeten D/A-Wandler (Familie DAC08-) werden üblicherweise mit bipolarer Versorgung (z.B. ± 5V) betrieben. Da eine negative Spannung nicht immer zur Verfügung steht, wurde hier ein "künstlicher Mittelpunkt" der +15 V - Versorgung erzeugt (Spannungsteiler R3/R4 und Spannungsfolger I30), der die "Masse" für I27 und I28 herstellt. Der Spannungsbereich für die Dateneingänge der DACs liegt dadurch zwischen +7,5 V (L) und +15 V (H); der notwendigen Pegelanpassung dienen die 16 Spannungsteiler mit den 100-kΩ-Widerständen. Da die DAC-Ausgänge (Pin 4) für Stromsteuerung ausgelegt sind, ist pro Kanal je ein Strom / Spannungswandler (I29, I30 mit den zugehörigen Widerständen) erforderlich. An den Ausgängen Pt11 und Pt12 stehen die Steuerspannungen für den Phasenschieber (Baugruppe DK1OF 046) mit passendem Pegel zur Verfügung.

7.3. Hinweise zum Nachbau

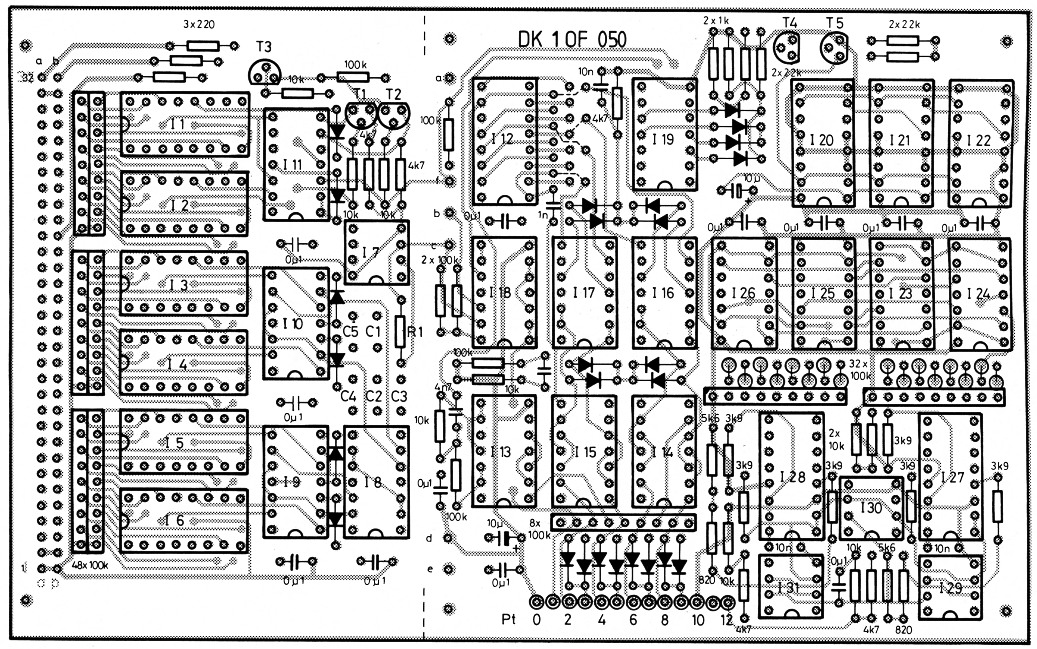

Für die beschriebene Schaltung wurde eine beidseitig geätzte, durchkontaktierte Leiterplatte entworfen. Sie hat Europa-Format (160 mm × 100 mm), trägt die Bezeichnung DK1OF 050 (!! von der Red.) und kann mit einer 64 poligen Steckerleiste versehen werden. Die genormte Bezeichnung der Steckkontakte stimmt mit Bild 37 überein; die Anschlüsse Pt0 bis Pt12 (Bilder 38 und 39) sind nicht über diese Leiste geführt, hier kann eine separate Steckverbindung eingesetzt werden. Will man die Baugruppe nur für Handbetrieb verwenden, dann kann man den Komparatorteil von der Platte abtrennen, um Platz zu sparen (alle Bauteile von Bild 37 entfallen). Bild 40 zeigt den Bestückungsplan für die Leiterplatte.

Bild 40: Bestückungsplan der Leiterplatte DK1OF 050

| T1,T2,T3,T4,T5 | BC413 oder ähnlicher |

| alle Dioden | 1N4148 oder ähnlicher |

| I1,I2,I3,I4,I5,I6 | CMOS 4585B oder 40085B |

| I7 | 7555 (Intersil; MOS-Version des 555) |

| I8 | CMOS 4066B |

| I9,I10,I11 | CMOS 4081B |

| I12 | CMOS 4040B |

| I13,I14,I15 | CMOS 4011B |

| I16,I17,I18,I19 | CMOS 4001B |

| I20,I21,I22 | CMOS 4516B |

| I23,I24 | CMOS 4077B |

| I25,I26 | CMOS 4070B oder 4030B |

| I27,I28 | DAC08, DAC0800 (Bezeichnung je nach Hersteller) |

| I29,I30,I31 | Op.-Verstärker 741 C, 8 pol. DIP-Gehäuse |

| Steckerleiste | Bauform C, DIN 41612, (Siemens) 64 polig z. B. C42334-A191-A521 |

| Federleiste | z. B. C42334-A192-A521 (Siemens) |

| Elkos | 10 µF / 25V Raster 5mm |

| übrige Kondensat. | ker. Scheiben oder Vielschichtkond., RM = 5 |

| Widerst. mit Punkt | 8 × 100 kΩ/0,1 W Raster 2,54 mm (9 Stück) |

| alle übrigen | ≥ 1/8 W, Raster 10 mm |

| LED1,LED2,LED3 | Leuchtdioden |

| S1,S2,S3,S4 | 4 Doppel- oder 8 Einzel-Drucktaster |

| S | Kippschalter 1 x ein |

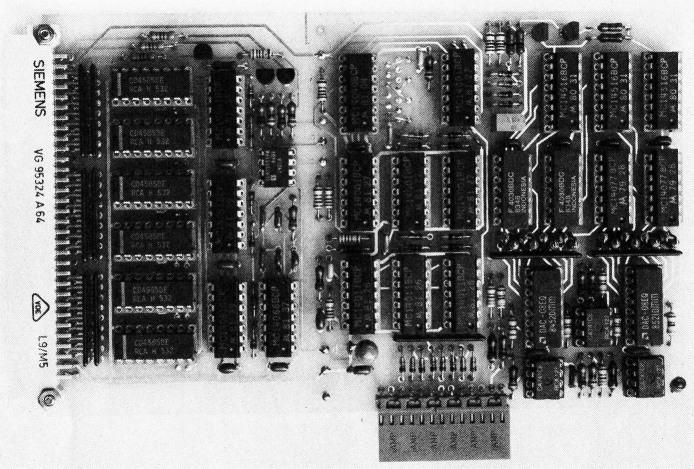

Zur Versorgung sind stabilisierte Spannungen von +5 V (Stromentnahme ohne Leuchtdioden: 45 mA) und +15V (20 mA) notwendig. Das Foto eines Musteraufbaus ist in Bild 41 zu sehen.

Bild 41: Ein Musteraufbau der Leiterplatte DK1OF 050.

7.4. Inbetriebnahme

Nachdem die Taster S1-S4, der Schalter S und die drei Leuchtdioden zunächst probeweise mit der Baugruppe verbunden wurden, kann man die Versorgungsspannungen anlegen. S steht vorläufig auf "Hand". Ein an Pin 10 von I12 angeschlossenes Oszilloskop muß ein sauberes Rechtecksignal (5 VSS) von etwa 8 kHz anzeigen (die genaue Frequenz ist unkritisch). Der an Pin1 abgegebene 2-Hz-Takt läßt sich notfalls auch mit einem Voltmeter überprüfen, wenn kein Oszillograf zur Verfügung steht. Drückt man kurz eine der Tasten, so wird man die unter 7.2. beschriebenen "Impulspakete" an Punkt C (oder am Kollektor von T5) beobachten können. Dauerndes Drücken muß ein konstantes Rechtecksignal zur Folge haben. Wird die Taste zur anderen Seite hin betätigt, dann muß sich der Logikpegel an D (bzw. am Kollektor von T4) ändern.

Anschließend verbindet man den Eingang des Oszillografen mit Pt 12. Drücken von S4 wird eine dreieckförmige Wechselspannung auf dem Schirm erscheinen lassen (Folgefrequenz etwa 16 Hz); die Spannungsminima sollen bei + 2V, die Maxima bei + 7V liegen (Toleranz: ± 0,5 V). Die "Kurve" muß glatt aussehen (natürlich besteht jede Rampe aus 256 gleichen Stufen); beobachtet man irgendwelche Sprünge, so deutet dies auf einen Fehler im Binärzähler, Decoder oder im DAC hin, der unbedingt aufzuspüren und zu beseitigen ist (defekter Chip, Zinnspritzer auf der Leiterplatte, Lötstelle vergessen etc.). Der Oszillator würde sich sonst nicht kontinuierlich abstimmen lassen. Dieser Test ist auch auf den zweiten Kanal (Ausgang Pt11) anzuwenden.

Steht kein Oszilloskop zur Verfügung, so muß man alle 512 Stufen langsam (mit S1) durchtakten und dabei die abgegebenen Spannungen an Pt 11 und Pt 12 mit einem Voltmeter beobachten.

Nun kann man die Ausgänge der Baugruppe mit den Anschlüssen Pt 9 und Pt 10 des Oszillatorbausteins DK 1 OF 046 verbinden und diesen in Betrieb setzen. Er muß sich nun über S1 bis S4 bedienen lassen. Ein Vertauschen der Steuerleitungen invertiert die Abstimmrichtung.

Nun bringen wir den Schalter S in Stellung "Automatik". Die Dateneingänge für Soll- und lstwert bleiben vorläufig offen (was wegen der eingebauten pull-down-Widerstände keine Gefahr für die Komparatoren bedeutet). LED1 wird leuchten, denn Istwert = Sollwert = 0. Legt man einen der Istwert-Eingänge probeweise auf +5 V, dann leuchtet LED 3 und die Oszillatorfrequenz wird niedriger (evtl. Pt11/Pt12 tauschen). Die Abstimmgeschwindigkeit hängt davon ab, an welcher Dekade der H-Pegel angelegt wurde (siehe Abschnitt 7.1.). Verbindet man einen der Sollwert-Eingänge mit +5 V, so muß LED 2 aufleuchten und die erzeugte Frequenz wird höher.

Zum Schluß wird der Frequenzzähler angeschlossen; seine BCD- Ausgänge verdrahtet man (in der richtigen Reihenfolge!) mit den Istwert-Eingängen der Komparatoren, die Sollwert-Eingänge führen zu einem Satz: Ziffernschalter (wenn das Computer-Interface noch nicht fertig ist). Wird hier nun ein Wert eingestellt, der im Abstimmbereich des Oszillators liegt, so muß die Automatik nun versuchen, die Oszillatorfrequenz auf diesen Wert einzuregeln. Gelingt dies nicht, sondern beobachtet man ein dauerndes Pendeln um den eingestellten Wert, so ist die Abstimmgeschwindigkeit des Regelkreises für die (gegebene) Meßhäufigkeit des Zählers zu hoch. In diesem Fall ist R1 so weit zu vergrößern, bis die Schaltung ordnungsgemäß einregelt und gerade noch kein Pendeln auftritt. Da die Torzeit des verwendeten Zählers der entscheidende Parameter ist, können diesbezüglich keine genaueren Dimensionierungshinweise gegeben werden. Die in Bild 37 angegebenen Werte für R1 und C1 bis C5 sind optimal für einen Zähler mit 10 Messungen/Sekunde. Für einen Sollweitsprung von 1 MHz wird eine Regelzeit von 15 Sekunden benötigt, bei einer Auflösung (niedrigste Dezimalstelle) von 100 Hz.

7.5. Geeignete Frequenzzähler

Für die beschriebene Baugruppe wurde zwar ein passender 6-stelliger Zähler (ohne Vorteiler bis 45 MHz verwendbar) entwickelt, die Leiterplatte ist jedoch nicht reif zur Veröffentlichung; außerdem wollte der Verlag dieser Zeitschrift nicht noch eine weitere Zählerversion ins Programm nehmen. Aber wie man gleich sehen wird, geht es auch anders.

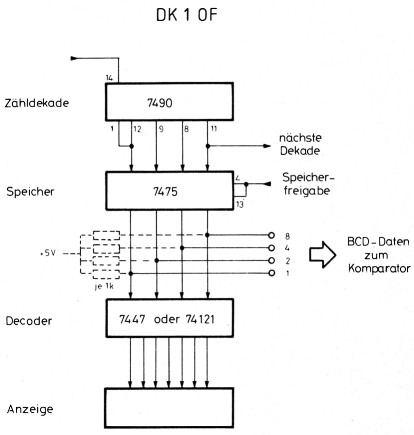

Gut geeignet für die hier diskutierte Anwendung sind alle älteren, mit TTL-Bausteinen diskret aufgebauten Modelle (z.B. DL 8 TM), wenn sie für das Latch (Anzeige-Speicher) und den Decoder (für Siebensegment- oder Nixie-Anzeigen) separate Chips verwenden. Wie man dabei vorzugehen hat, soll Bild 42 verdeutlichen. Der von TTL-Bausteinen angebotene H-Pegel von + 3 bis 4 V ist zur Ansteuerung von CMOS-Eingängen etwas knapp. Es empfiehlt sich deshalb, die TTL-Ausgänge über 1-kΩ-pull-up-Widerstände mit +5 V zu verbinden. Dies sollte man generell bei TTL→CMOS-Übergängen tun.

Bild 42: Abnahme der BCD-Daten aus einem Zähler

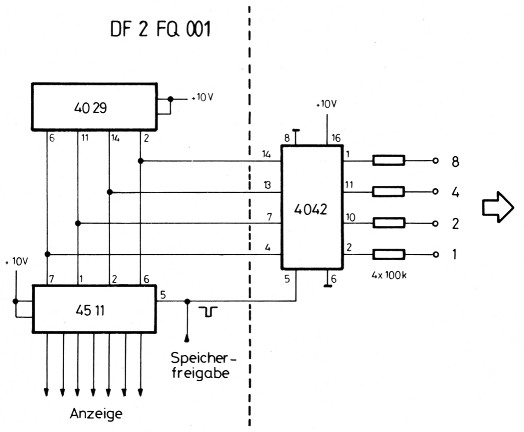

Auch der in (4) beschriebene Verrechnungszähler läßt sich verwenden, wenn er mit einem zusätzlichen Latch ausgestattet wird. Bild 43 zeigt einen Schaltungsauszug. Es wurde nur eine Dezimalstelle gezeichnet, mit den übrigen verfährt man in gleicher Weise. Da der Zähler mit +10 V versorgt wird, sind an den Datenausgängen Serienwiderstände vorzusehen. Diese bilden mit den pull-down-Widerständen an den Komparator-Eingängen Spannungsteiler, so daß der richtige H-Pegel von +5 V dort erscheint. Der Baustein von DF2FQ ist vierstellig ausgeführt, was für Funkgeräte im allgemeinen ausreicht (100 Hz Auflösung bei Kurzwelle, 1 kHz bei VHF/UHF). Die Eingänge der beiden höchstwertigen Stellen des Komparators bleiben daher unbeschaltet.

Bild 43: BCD-Ausgänge am DF2FQ - Zähler.

Der in (5) beschriebene Zähler verwendet einen hochintegrierten Baustein, den man nur mit erheblichem Aufwand zur Abgabe von parallelen BCD-Daten veranlassen kann (außer man verzichtet auf die Voreinstellung). Da auch dieser nur vierstellig aufgebaut ist, bietet er gegenüber (4) keine Vorteile.

Literatur

- J. Kestler: PLL-Oszillatoren mit Verzögerungsleitung 1, UKW-Berichte 24 (1984) Heft 3, S. 130-139

- J. Kestler: PLL-Oszillatoren mit Verzögerungsleitung 2, UKW-Berichte 24 (1984) Heft 4, S. 195-203

- J. Kestler: PLL-Oszillatoren mit Verzögerungsleitung 3, UKW-Berichte 25 (1985) Heft 1, S. 13-21

- H. Eckard: Ein 45-MHz-Verrechnungszähler, UKW-Berichte 20 (1980) Heft 3, S. 147-151

- J. Kestler: Ein setzbarer Vor/Rück-Frequenzzähler, UKW-Berichte 20 (1980) Heft 4, S. 210-221

Teil 1 - Teil 2 - Teil 3 - Teil 4 - Teil 5

DK1OF, Joachim Kestler.